Системный агент: контроллер памяти DDR3, PCU и другие

Ранее вместо определения System Agent в терминологии Intel фигурировало так называемое «Неядро» - Uncore, то есть, «всё, что не входит в Core», а именно КЭШ L3, графика, контроллер памяти, другие контроллеры вроде PCI Express и т.д. Мы же по привычке частенько называли большую часть этого элементами северного моста, перенесённого из чипсета в процессор.

Системный агент микроархитектуры Sandy Bridge включает в себя контроллер памяти DDR3, модуль управления питанием (Power Control Unit, PCU), контроллеры PCI-Express 2.0, DMI, блок видеовыхода и пр. Как и все остальные элементы архитектуры, системный агент подключен в общую систему посредством высокопроизводительной кольцевой шины.

Архитектура стандартной версии системного агента Sandy Bridge подразумевает наличие 16 линий шины PCI-E 2.0, которые также могут быть распределены на две шины PCI-E 2.0 по 8 линий, или на одну шину PCI-E 2.0 на 8 линий и две шины PCI-E 2.0 по четыре линии. Двухканальный контроллер памяти DDR3 отныне «вернулся» на кристалл (в чипах Clarkdale он располагался вне процессорного кристалла) и, скорее всего, теперь будет обеспечивать значительно меньшую латентность.

Тот факт, что контроллер памяти в Sandy Bridge стал двухканальным, вряд ли обрадует тех, кто уже успел вывалить немалые суммы за оверклокерские комплекты трёхканальной памяти DDR3. Что ж, бывает, теперь будут актуальны наборы лишь из одного, двух или четырёх модулей. По поводу возвращения к двухканальной схеме контроллера памяти у нас имеются кое-какие соображения. Возможно, в Intel начали подготовку микроархитектур к работе с памятью DDR4? Которая, из-за ухода от топологии «звезды» на топологию «точка-точка» в версиях для настольных и мобильных систем будут по определению только двухканальной (для серверов будут применяться специальные модули-мультиплексоры). Впрочем, это всего лишь догадки, для уверенных предположений пока что недостаточно информации о самом стандарте DDR4. Расположенный в системном агенте контроллер управления питанием отвечает за своевременное динамичное масштабирование напряжений питания и тактовых частот процессорных ядер, графического ядра, КЭШей, контроллера памяти и интерфейсов. Что особенно важно подчеркнуть, управление питанием и тактовой частотой производится независимо для процессорных ядер и графического ядра.

Совершенно новая версия технологии Turbo Boost реализована не в последнюю очередь благодаря этому контроллеру управления питанием. Дело в том, что, в зависимости от текущего состояния системы и сложности решаемой задачи, микроархитектура Sandy Bridge позволяет технологии Turbo Boost «разогнать» ядра процессора и встроенную графику до уровня, значительно превышающего TDP на достаточно долгое время. И действительно, почему бы не воспользоваться такой возможностью штатно, пока система охлаждения ещё холодная и может обеспечить больший теплоотвод, чем уже разогретая?

Кроме того, что технология Turbo Boost позволяет теперь штатно «разгонять» все четыре ядра за пределы TDP, также стоит отметить, что управление производительностью и тепловым режимом графических ядер в чипах Arrandale/Clarkdale, по сути, только встроенных, но не до конца интегрированных в процессор, производилось с помощью драйвера. Теперь, в архитектуре Sandy Bridge, этот процесс также возложен на контроллер PCU. Такая плотная интеграция системы управления напряжением питания и частотами позволила реализовать на практике гораздо более агрессивные сценарии работы технологии Turbo Boost, когда и графика, и все четыре ядра процессора при необходимости и соблюдении определённых условий могут разом работать на повышенных тактовых частотах со значительным превышением TDP, но без каких-либо побочных последствий.

Принцип работы новой версии технологии Turbo Boost, реализованной в процессорах Sandy Bridge, отлично описывается в мультимедийный презентации, показанной в сентябре на Форуме Intel для разработчиков в Сан-Франциско. Представленный ниже видеоролик с записью этого момента презентации расскажет вам о Turbo Boost быстрее и лучше, чем любой пересказ.

Каждое из четырёх ядер Sandy Bridge может быть при необходимости независимо переведено в режим минимального энергопотребления, графическое ядро также можно перевести экономичный режим. Кольцевая шина и КЭШ L3, в силу их распределения между другими ресурсами, не могут быть отключены, однако для кольцевой шины предусмотрен специальный экономичный ждущий режим, когда она не нагружена, а для КЭШ-памяти L3 применяется традиционная технология отключения неиспользуемых транзисторов, уже известная нам по предыдущим микроархитектурам. Таким образом, процессоры Sandy Bridge в составе мобильных ПК обеспечивают длительную автономную работу при питании от аккумулятора. Модули видеовыхода и мультимедийного аппаратного декодирования также входят в число элементов системного агента. В отличие от предшественников, где аппаратное декодирование было возложено на графическое ядро (о его возможностях мы поговорим в следующий раз), в новой архитектуре для декодирования мультимедийных потоков используется отдельный, гораздо более производительный и экономичный модуль, и лишь в процессе кодирования (сжатия) мультимедийных данных используются возможности шейдерных блоков графического ядра и КЭШ L3. Предусмотрены инструменты воспроизведения 3D-контента: аппаратный модуль декодирования Sandy Bridge способен без труда обрабатывать сразу два независимых потока MPEG2, VC1 или AVC в разрешении Full HD.

Таким образом, развитие ставшей традиционной архитектуры показано выше. Однако, процессоры с одной инструкцией в команде имеют свой потолок быстродействия. Будущее многим аналитикам видится в архитектуре команд с множественным числом инструкций – VLIW архитектуре. Компиляторы и разработчики команд сами подготавливают параллельные процессы, снимая напряженный режим проверки условия Рассела-Нарьяни с исполнительных устройств. Выше преимущества этих архитектур рассмотрены для архитектуры IA-64 – три поля инструкций и ЦПС - TMS320C6411 – восемь полей инструкций.

Большая перспектива и в распределенной обработке данных, решении фрагментов задач в сетевых средах майнфреймов и супер компьютеров. Кластер "СКИФ К-500", построенный в рамках совместной белорусско-российской программы "СКИФ" по развитию вычислительной техники, стал первой системой, созданной отечественными специалистами на базе архитектуры Intel, вошедшей в престижный список TOP500 самых производительных компьютерных систем планеты. Основой кластера стали 128 процессоров Intel Xeon с тактовой частотой 2,8 ГГц, которые объединены в 64 двухпроцессорных вычислительных узла, обладающих емкостью дисковой подсистемы в размере 60 ГБ каждый (общая емкость дисковой системы, таким образом, составляет 3840 ГБ). Кластер располагает 128 ГБ оперативной памяти, а его пиковая производительность составляет 716,8 гигафлопс (миллиардов операций с плавающей запятой). Кластер сдан в эксплуатацию в сентябре 2003 года. Предполагается, что кластер будет использоваться для высокопроизводительных вычислений в наукоемких отраслях промышленности, биологии, медицине, генетике, геологоразведке, для контроля за окружающей средой, прогнозирования погоды, решения транспортных и многих других задач. В ряде организаций и университетах Республики устанавливаются суперкомпьютеры. В БГУ суперкомпьютер "СКИФ К-1000-05" установлен в 2010 г.

Видеоадаптеры

Вывод на экран монитора графической информации и 3D сцен, потоков видео, стереоизображений это далеко не полный перечень задач решаемых GPU современных видеоадаптеров. Это объемные сложные задачи сильно насыщенные математикой. Их решение всегда определяло уровень КС. Ниже на рис.14.1 и 14.2. показаны два важных расчета проводимых в графических конвейерах GPU - геометрии и растеризации.

Рис. 14.1. Расчет геометрии

Рис. 14.2. Обработка фрагментов.

Приступая к разработке нового поколения 3D архитектуры 2002 года, перед инженерами NVIDIA было решено поддержать аппаратно расчеты физических эффектов и интенсивных вычислений с плавающей запятой, улучшить конвейеры GPU при работе с потоками и геометрией, с учётом достижения максимальной производительности при работе с приложениями, использующими прежние OpenGL, DirectX 9 и ранние версии DirectX. Появилась новая архитектура с внушительной матрицей 32-х сдвоенных процессоров - GeForce 8800 на многие годы ставшая базой новых решений, поддерживающая и параллельные расчеты в физике.

Новая архитектура поддержала унифицированные шейдеры и состояла из 128 обособленных, совершенно самостоятельных потоковых процессоров с тактовой частотой до 1,35 ГГц. Каждый конвейер-процессор, в свою очередь, способен динамически перестраиваться для обработки вершин, пикселей и выполнения геометрических или физических операций, обеспечивая таким образом пиковую загрузку ресурсов GPU и максимальную сбалансированную гибкость при обработке шейдерных задач.

Рис. 14.3. Возможности процессоров

Одноядерный дизайн GeForce 8800 позволяет значительно увеличить производительность при работе с современными приложениями и масштабировать некоторые Шейдерные операции.

Классическая модель конвейера, задействованного на обработку потока данных с рядом атрибутов, индексов, команд и текстур, направляемых центральным процессором в графический чип включает в себя: расчеты вершинных и пиксельных шейдеров, растрирование и финальная запись пикселей во фреймовый буфер (рис. 14.4).

В отличие от классического дискретного дизайна, в случае унифицированной архитектуры GeForce 8800, появляется возможность значительным образом снизить количество задействованных стадий конвейера и изменить линейную последовательность обработки потока данных, придав ей более цикличный характер. Таким образом, входящие данные поступают на вход унифицированного шейдерного модуля, по выходу записываются в регистры и затем вновь подаются на вход модуля для исполнения следующей операции обработки. На (рис. 14.5) показаны классические конвейеры, обрабатывающие дискретные шейдеры.

Рис. 14.4. Конвейеры, обрабатывающие дискретные шейдеры

Заложенное в архитектуру GeForce 8800 количество аппаратных шейдерных модулей будет особенно востребовано при работе с 3D. Разработчики NVIDIA GeForce 8800 полагают, что такая архитектура окажется более удачной при сбалансированном распределении нагрузки, для эффективной загрузки чипа при работе под DirectX 10 и с любой моделью API.

На пример, пусть идет интенсивная прорисовка геометрии – мощная обработка вертексных шейдеров. Производительность определится числом вертексных модулей. Пусть, более сложная обработка световых эффектов на воде потребует более интенсивной работы пиксельных шейдеров, и здесь максимальная производительность также определиться числом модулей обработки пиксельных шейдеров. В обоих случаях до полной загрузки чипа и рачительного расхода энергии далеко, поскольку часть чипа так или иначе простаивает.

В случае унифицированной шейдерной архитектуры возрастает не только загрузка чипа, но также и производительность – за счёт полного перераспределения ресурсов на требуемую в данный момент задачу - обработку пиксельных или вертексных шейдеров.

Рис. 14.5. Конвейеры, обрабатывающие дискретные шейдеры

Унифицированные потоковые процессоры (Unified Streaming Processors, SP) ядра чипа GeForce 8800, представляющие собой процессоры общего назначения для обработки данных с плавающей запятой. Они могут обрабатывать геометрические, вертексные, пиксельные шейдеры, рассчитывать физические модели объектов. Объединяясь в группы, такие процессоры способны обеспечить впечатляющую параллельную вычислительную мощь.

Рис. 14.6. показывает сбалансированность архитектуры GeForce 8800, в которой блок потоковых процессоров SP объединён с блоками КЭШа, фильтрации текстур (Texture Filtering, TF) и адресации текстур (Texture Addressing, TA). 128 таких универсальных потоковых процессорных конвейера объединены в "подмножества".

На ранних стадиях разработки архитектуры GeForce 8800 было оценено то, что традиционная векторная архитектура менее эффективно использует вычислительные ресурсы, нежели скалярный дизайн процессорных модулей, особенно в случае обработки сложных смешанных шейдеров, сочетающих векторные и скалярные инструкции. Тем более что достаточно сложно добиться эффективной обработки и компиляции скалярных вычислений с помощью векторных конвейеров.

Рис. 14.6. Объединение SP,КЭШ и текстурных фильтров и систем адресации

Традиционные векторные графические чипы - как от NVIDIA, так и от ATI (основной конкурент Nvidea на рынке GPU, сейчас влита в AMD), обладают аппаратной реализацией шейдеров с поддержкой двойного исполнения инструкций. Так, чипы ATI с дизайном "3+1" допускают исполнение единой 4-элементной векторной инструкции или парной операции из трёхэлементной векторной инструкции и скалярной инструкции. Чипы серий NVIDIA GeForce 6x и GeForce 7x поддерживают парное исполнение инструкций вида 3+1 и 2+2. Архитектуры GeForce 8800 загружает скалярными инструкциями модули чипа со 100% эффективностью.

Векторный шейдерный программный код преобразуется в скалярные операции непосредственно чипом GeForce 8800. Таким образом, с помощью скалярной архитектуры на базе 128 скалярных вычислительных модулей теоретически можно добиться 2-кратного увеличения производительности против системы из 32 4-компонентных векторных процессорных модулей.

Чипы серии GeForce 8800 поддерживают процесс HDR (High Dynamic Range) рендеринга с 128-битной точностью, не только в режиме FP16 (64-битный цвет), но и FP32 (128-битный цвет), которые могут обрабатываться одновременно с процессом мультисэмплированного антиалиазинга). Это позволяет добиться реалистичных эффектов освещения и наложения теней, при этом обеспечивается высокая динамика и детализация самых затемнённых и самых светлых объектов.

Рис. 14.7. На рисунке слева, результаты изотропного множественное трилинейного текстурирования (Isotropic Trilinear MipMapping), справа – анизотропного множественного трилинейного текстурирования (Anisotropic Trilinear MipMapping)

На рис. 14.7 приведён пример работы анизотропной фильтрации (Anisotropic Filtering, AF), позволяющей добиться большей чёткости и резкости различных объектов, расположенных под острым углом и/или уходящих в перспективу. В комбинации с технологией множественного трилинейного текстурирования (с изменяющимся по мере удаления разрешением, trilinear mipmapping), анизотропная фильтрация позволяет снизить масштаб искажений и сделать картинку значительно чётче.

Анизотропная фильтрация чувствительна к пропускной способности шины памяти. К примеру, режим 16xAF означает 16 билинейных считываний на каждый из двух смежных уровней множественного текстурирования (в сумме 128 обращений к памяти), усложнённых получением финальной по пиксельной цветовой текстуры. Решения на базе чипов GeForce 8800 получили новую опцию в панели управления AF, названную Angular LOD Control и имеющую два режима - Quality и High Quality. На рис. 14.8 показаны изменения в анизотропной фильтрации для старой и новых архитектур.

Рис. 14.8. AF у GeForce 7 (слева) против GeForce 8 с Angular LOD Texture Filtering в режиме High Quality (справа)

Особенно важно получение на GPU нового качества - Quantum Effects – ускорение расчетов физических моделей объектов и процессов.

Процессоры GeForce 8800 GTX в количестве 128 обеспечивают достаточный уровень мощности вычислений с плавающей запятой для достижения ряда новых реалистичных эффектов вроде дымки, огня, взрывов; реалистичной имитации движущихся волос, меха, воды. Такие возможности заинтересовали многих потребителей, в том числе, и разработчиков супер компьютеров.

Технология NVIDIA PureVideo HD, позволяет обеспечить высокое качество и плавное воспроизведение HD Video контента с носителей HD DVD и Blu-ray, при минимальном использовании ресурсов центрального процессора.

Все карты GeForce 8800 поддерживают игровые установки Extreme High Definition (XHD), при этом игры могут запускаться в широкоформатных режимах вплоть до 2560x1600 – это в семь раз превышает качество картинки HD телевизора 1080i и в два раза - HD формата 1080p.

Несвязанный обсчёт шейдеров, ветвление и Early-Z.

На адресацию текстур, выборку и фильтрацию уходит определённое количество тактов GPU, и в случае необходимости выборки и фильтрации текстуры до выполнения следующей операции обсчёта в определённом шейдере, латентность этого процесса (например, в случае 16x AF) могут значительно замедлить работу GPU. В архитектуре GeForce 8800 предусмотрен щадящий режим работы и механизм "скрытия" латентности текстурной выборки с помощью одновременного исполнения ряда независимых математических операций. Если в пиксельном конвейере GeForce 7 обсчёт адреса текстуры перемежается с математическими FP шейдерными операциями, в модуле Shader Unit 1, то несвязанная независимая работа в шейдерными и текстурными операциями в GeForce 8800 снимает проблему (рис. 14.9).

Рис. 14.9. Улучшение конвейеров обработки шейдеров в новой архитектуре

Архитектура GeForce 8800 аппаратно поддерживает процессы ветвления на 16 пикселей (тредов), в некоторых случаях – на 32 пикселя.

Рис. 14.10. Улучшение эффективности сортировки пикселей по Z (цвет)

Рис. 14.11. Улучшение эффективности сортировки пикселей по Z (тень)

Z-буфера GeForce 8800 сортируют пикселя со скоростью, в четыре раза превосходящей этот процесс у GeForce 7900. GPU имеет возможность обрабатывать более сложные ситуации на уровне каждого пикселя. Z-сравнения данных о каждом пикселе производятся в модуле растеризатора - ROP (raster operations). Для увеличения производительности чипы GeForce 8800 поддерживают технологию Early-Z, позволяющую определить Z-значения пикселей до того как они поступают на конвейер пиксельного шейдера, благодаря этому увеличивается производительность и не производится ряд заведомо ненужных операций. Пример работы Early-Z показан на рис. 14.10 и 14.11.

Ключевой момент – контроллер памяти. Чипы GeForce 8800 обладают шестью подразделами контроллера памяти, каждый из которых имеет 64-битный интерфейс, что в сумме даёт 384-битную ширину комбинированной интерфейсной шины памяти. Таким образом, получается 768 Мб скоростной памяти, при этом поддерживается память стандартов до GDDR4. Видеокарты GeForce 8800 GTX оснащены памятью GDDR3 с тактовой частотой по умолчанию 900 МГц (1800 МГц DDR), что при 384-битной ширине интерфейса даёт пропускную способность до 86,4 Гб/с.

Потоковый вывод данных позволяет отправлять данные, генерируемые геометрическими (или вертексными) шейдерами в буферы памяти и затем возвращать их и загружать в начало конвейера GPU для последующей обработки.

Развитие архитектуры GPU продолжается. В 2010 году выпущен чип GF100 (GPU nVidia GeForce GTX 480). Он насчитывает 480 потоковых процессоров и на плате адресуется к 1 536 Мб памяти GDDR5 с 384-битной шиной. Тактовые частоты ядра и памяти не уточняются (для базового варианта акселератора они составляют 700 и 1 848 МГц соответственно). MSI N480GTX обладает поддержкой программного интерфейса DirectX 11 и технологий PhysX, CUDA и 3D Vision Surround. Для подключения устройств отображения информации есть интерфейсы Dual-DVI и HDMI; возможна работа в режиме 3-way SLI (режим объединяющие видеадапторы в кластер с внутренней скоростной шиной). В GPU применены компоненты «военного класса» (Military Class), обеспечивающие высокую стабильность и надежность.

Микроконтроллеры

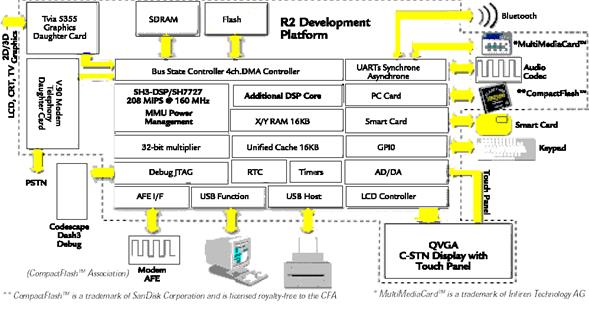

Микроконтроллеры появились одновременно с процессорами Intel 8008. Их модификации, разновидности (рис. 15.2) насчитывают несколько десятков названий. Всех их выделяет развитая архитектура входных и выходных портов. По разрядности мы увидим 4-х, 8-ми,16-ти, 32-х, 64-х разрядные процессоры. Ряд из них поддерживает виртуальную память, имеет встроенные КЭШ данных команд. По производительности они перешли рубеж в 1 Гига операций в секунду. Однако они дешевы, не требуют специальных систем охлаждения и следовательно встраиваемы в «глаза» роботов, поздравительные открытки. Они неизбежный атрибут любой компьютерной системы и существуют в ней в количестве десятков, сотен экземпляров. Например, на рис. 15.1 показаны места установки микроконтроллеров в современном автомобиле. Рис. 15.3 показывает подключение различных устройств к 32-х разрядному контроллеру.

Рис. 15.1. Место микроконтроллеров в изделиях современной техники на примере автомобиля.

Рис. 15.2. Гибкость микроконтроллеров на примере линейки М16_М32.

Рис. 15.3. Комплексный охват возможных наборов внешних устройств на примере 32-х разрядного микропроцессора SH3-DSP SH7727.

В микроконтроллерах, как в миниатюрных зеркалах отражаются многие ключевые принципы формирования архитектуры компьютерных систем. Это же касается и методики программирования КС. Однако рабочие программы микроконтроллеров более стабильны и менее ориентированы на будущие изменения в окружении микроконтроллера, чем стандартные пакеты программ в КС на базе РС. Выбор типа микроконтроллера предполагает предварительный анализ параметров потоков данных и алгоритмов управления внешними устройствами. Современный рынок микроконтроллеров предлагает множество возможных решений. Остановимся на изучении специфики двух групп.

Признанным лидером в мире микроконтроллеров 8-разрядной архитектуры является архитектура MCS-51/151/251 фирмы Intel. Число клонов этой модели исчисляется многими десятками типов БИС. Практически она встраивается и в состав различных СБИС, как, например, АЦП AduC812_0 фирмы Analog Devices. Документы AduC812_0.pdf, Assemble.pdf, Simulate.pdf позволяют подробно изучить данное семейство. Программы Wavrasm и Wavrsim помогут написать и отладить программы для устройств на базе данной архитектуры.

Среди микроконтроллеров, претендующих на более высокие планки функциональных возможностей и быстродействия, выделяется серия SuperH фирмы Hitachi), тактовые частоты семейства достигли в 1999 г. отметки – 100 МГц). Младший представитель данного семейства рассматривается ниже.

H8/3002 - микроконтроллер с ядром H8/300H базовой Hitachi архитектуры. H8/300H - центральный процессор имеет 32-битовую внутреннюю архитектуру с шестнадцатью 16-битовыми регистрами общего назначения (могут использоваться как шестнадцать 8-битовых регистров или восемь 32-битовых). Процессор квази RISC архитектуры (на 16 МГц - время выполнения команд Add/subtract: 125 ns, Multiply/divide: 875 ns). Может адресовать 16-Мбайт линейного пространства. Система команд совместимая снизу вверх в уровне объектного кода с H8/300, позволяя переносить ПО на чипы H8/300 серии.

H8/3002 (рис. 15.4) включает RAM, 16-битовй таймер (ITU), программируемый контроллер синхронизации (TPC), таймер (WDT), последовательный интерфейс (SCI), A/D - АЦП, порты I/O, контроллер прямого доступа в память (DMAC), контроллер регенерации R… c… и другие средства. Четыре режима (MCU) назначают ширину шины данных и размер адресного пространства.

Рис 15.4. Структура микроконтроллера H8/3002

Поддерживает режимы:

1. нормальный режим (64-кбайт пространства адреса, доступного вне чипа H8/3002);

2. широкий режим (16-Мбайт пространства адреса)

3. Характерные инструкции:

4. 8/16/32-битовая пересылка данных,

5. практически полный набор 8/16/32-битовых арифметических и логических инструкций,

6. знаковое и без знаковое умножение (8 бит на 8 бит, 16 бит на 16 бит),

7. знаковое и без знаковое деление (16 бит на 8, 32 бита на 16),

8. побитовые инструкции аккумулятора,

9. поразрядные операции с регистрово-косвенным указанием позиций.

RAM: 512 байта.

Прерывание:

- Семь внешних контактов прерываний (IRQ 0…5),

- 30 внутренних прерываний,

- три уровня приоритета.

Контроллер шины:

- пространство адреса может разделяться на восемь областей, с независимой спецификацией шины в каждой области;

- Chip select доступен для областей 0 – 3 DRAM;

- 8- или 16-битовое смещение для каждой области;

- двух- или трех - уровневый доступ для каждой области;

- выбор четырех способов ожидания;

арбитраж шины.

Регенерация DRAM:

- допускает непосредственное подключение 16-битового DRAM;

- CAS -перед- RAS;

- метод избирательной регенерации позволяет подключать псевдо-статическое RАМ;

- метод избирательной регенерации пригоден для повторного запуска таймера интервала.

Контроллер прямого доступа в память (DMAC).

Короткий режим адреса:

- доступно до четырех каналов,

- выбор режима I/O (холостой режим, или режим повторения),

- может активизироваться сравнением match/input прерываний из ITU каналов 0 - 3, SCI прерывания - передатчик данных пуст и приемник данных заполнен.

Режим полного адреса внешнего запроса:

- максимум два канала доступно,

- выбор нормального или блочного режима передачи.

- активизируется сравнением match/input прерываний из ITU каналов 0…3, внешними запросами, или автозапросом контроллера DMA (DMAC).

16-bit таймеры (ITU):

- пять 16-битовых канала, способные вырабатывать до 12 выходных импульсных последовательностей и принимать до 10 входных импульсных последовательностей;

- 16-битные счетчики (каналы 0 - 4);

- два мультиплексных выходных compare/input (каналы 0 - 4);

- функционирование может быть синхронизировано (каналы 0 - 4);

- режим широтно-импульсной модуляции PWM (каналы 0 - 4);

- фаза, режим счета доступен (канал 2);

- буферизация (каналы 3 и 4);

- синхронизованный по сбросу режим PWM (каналы 3 и 4);

- дополнительный режим PWM (каналы 3 и 4);

- DMAC может активизироваться сравнением match/input через прерывание А (каналы 0 - 3).

Программируемый контроллер синхронизации (TPC):

- максимум 16-фазный выход, использует ITU как базу времени;

- четыре 4-фазных выхода (или одна 16 - фазная группа, или две 8-фазных);

- доступен режим Non-overlap;

- выходные данные могут передаваться DMAC.

Таймер интервала (WDT):

- сигнал Reset может генерироваться данным таймером;

- сигнал Reset может поступить с внешнего входа (1 канал);

- пригоден и как таймер интервала.

Последовательный интерфейс (SCI):

- асинхронной или синхронной способ связи;

- полный дуплекс;

- в чипе 2 канала.

АЦП (А/D):

- разрешение - 10 бит;

- восемь каналов, с выбором одного или нескольких (в режиме сканирования);

- конверсионное опорное напряжение;

- схема выборки / хранения;

- оцифровка за 8 мкс;

- возможность внешнего запуска.

Порты ввода/вывода (I/O):

- 38 линий ввода вывода;

- 8 линий только ввод.

Назначение выводов и конструктивные особенности микроконтроллера смотри в H8/3002 Hardware Manual (файл Akrobat Reader – H83_020h.pdf). Как видим только перечисление возможностей контроллера достаточно велико.

Сведения об основных регистрах приведены ниже.

Рис. 15.5. Основные регистры процессора

Системные регистры ЦП не рассматриваются в данной работе.

Восемь, ниже перечисленных, способов адресации поддерживаются процессором:

— Register direct [Rn]

— Register indirect [@ERn]

— Register indirect with displacement [@(d:16, ERn) or @(d:24, ERn)]

— Register indirect with post-increment or pre-decrement [@ERn+ or @–ERn]

— Absolute address [@aa:8, @aa:16, or @aa:24]

— Immediate [#xx:8, #xx:16, or #xx:32]

— Program-counter relative [@(d:8, PC) or @(d:16, PC)]

— Memory indirect [@@aa:8].

Пространство адресов расписано ниже (рис. 3.4 и рис. 3.5)

Рис. 15.6. Конфигурация регистров

Рассмотрим отдельные регистры устройств: адреса и назначение.

Модель блока таймеров (ITU) сложнее модели Interrupt Controller, портов – проще. Выбор микроконтроллера для конкретной разработки достаточно сложная задача. Стандартные вопросы: объем ОЗУ, ППЗУ, разрядность и быстродействие АЦП, ЦАП, количество портов ввода/вывода и т.п. требуют детального анализа эффективности принимаемых решений. H4sf5a95.pdf входящий в комплект документов, прилагаемых к лабораторной работе, позволит Вам разобраться в гибкости предложений по структуре на примере 4-битовых микроконтроллеров фирмы Hitachi.

Первым шагом в применении микроконтроллеров обычно является создании небольших универсальных плат с окружением микроконтроллера аналоговыми, цифровыми, импульсными входами/выходами.

Небольшой модуль на микропроцессоре H8 (рис. 15.8) обеспечивает доступ в Internet (рис. 15.9), снабжен последовательным интерфейсом (RS-232) для связи с компьютером, допускает использование внешнего модема. Пользователи могут управлять дистанционными устройствами на веб страницах через JavaScript и Java приложения. Модуль обеспечивает обмен по сети I2C, оптимизирован для контрольно-измерительной аппаратуры, промышленной, и домашней автоматики, имеет возможность подключения линейного ССД фотоприемника и т. п.

Рис. 15.7. Адресное пространство процессора

| Связь по SLIP, ICPM, TCP/IP, http, речевая команда; 16K FLASH; программирование ESP, HTML with JavaScript, VBScript, Java; цифровых выходов – 8; цифровых входов – 6; аналоговых входов – 8; I2C - мастер;RS-232 шина; 56 мм на 25 мм. |  |

| Рис. 15.8. Печатная плата с микропроцессором |

Рис. 15.9. Связи микропроцессора

Рис.15.10. Структура развитой системы гибких модульных средств

Многофункциональные модульные средства с перестраиваемой архитектурой (МСПА) являются основным рабочим средством автоматизации производства и научных исследований. Разработчики и изготовители технологического оборудования при выборе цифровой среды контроля и управления отдают предпочтение открытым системам, в первую очередь МСПА.

На рис.15.10 приведена структура развитой системы гибких модульных средств, построенная на основе линий передачи данных (верхний уровень иерархии – шина USB2), шин транспорта средней производительности (сеть средней производительности - USB1) и сети нижнего уровня.

Производительность сети верхнего уровня (порядка 50 Мбайт в секунду) обеспечивает транспорт потоков данных как между модулями с высокой вычислительной загрузкой, так и высокоскоростными приборами, например,

цифровыми телекамерами. Сегодня наметилась тенденция к реализации верхнего уровня иерархии системы на базе компьютеров общего применения как более дешевого варианта комплектации системы. Данный уровень иерархии, как правило, можно установить в отапливаемом помещении с нормальными климатическими условиями, в которых реально обеспечивается надежность работы PC.

Средний уровень системы обладает достаточной вычислительной мощностью для решения задач управления и контроля в реальном времени, и на верхний уровень поступает информация, чаще всего, статистического характера.

Производительность КС

Основу для сравнения различных типов компьютеров между собой дают стандартные методики измерения производительности. В процессе развития вычислительной техники появилось несколько таких стандартных методик. Они позволяют разработчикам и пользователям осуществлять выбор между альтернативами на основе количественных показателей, что дает возможность постоянного прогресса в данной области.

Единицей измерения производительности компьютера является время: компьютер, выполняющий тот же объем работы за меньшее время является более быстрым. Время выполнения любой программы измеряется в секундах. Часто производительность измеряется как скорость появления некоторого числа событий в секунду, так что меньшее время подразумевает большую производительность.

Однако в зависимости от того, что мы считаем, время может быть определено различными способами. Наиболее простой способ определения времени называется астрономическим временем, временем ответа (response time), временем выполнения(execution time) или прошедшим временем (elapsed time). Это задержка выполнения задания, включающая буквально все: работу процессора, обращения к диску, обращения к памяти, ввод/вывод и накладные расходы операционной системы. Однако при работе в мультипрограммном режиме во время ожидания ввода/вывода для одной программы, процессор может выполнять другую программу, и система не обязательно будет минимизировать время выполнения данной конкретной программы.

Для измерения времени работы процессора на данной программе используется специальный параметр - время ЦП (CPU time), которое не включает время ожидания ввода/вывода или время выполнения другой программы. Очевидно, что время ответа, видимое пользователем, является полным временем выполнения программы, а не временем ЦП. Время ЦП может далее делиться на время, потраченное ЦП непосредственно на выполнение программы пользователя и называемое пользовательским временем ЦП, и время ЦП, затраченное операционной системой на выполнение заданий, затребованных программой, и называемое системным временем ЦП.

В ряде случаев системное время ЦП игнорируется из-за возможной неточности измерений, выполняемых самой операционной системой, а также из-за проблем, связанных со сравнением производительности машин с разными операционными системами. С другой стороны, системный код на некоторых машинах является пользовательским кодом на других и, кроме того, практически никакая программа не может работать без некоторой операционной системы. Поэтому при измерениях производительности процессора часто используется сумма пользовательского и системного времени ЦП.

В большинстве современных процессоров скорость протекания процессов взаимодействия внутренних функциональных устройств определяется не естественными задержками в этих устройствах, а задается единой системой синхросигналов, вырабатываемых некоторым генератором тактовых импульсов, как правило, работающим с постоянной скоростью. Дискретные временные события называются тактами синхронизации (clock ticks), просто тактами (ticks), периодами синхронизации (clock periods), циклами (cycles) или циклами синхронизации (clock cycles).Разработчики компьютеров обычно говорят о периоде синхронизации, который определяется либо своей длительностью (например, 10 наносекунд), либо частотой (например, 100 МГц). Длительность периода синхронизации есть величина, обратная к частоте синхронизации.

Таким образом, время ЦП для некоторой программы может быть выражено двумя способами: количеством тактов синхронизации для данной программы, умноженным на длительность такта синхронизации, либо количеством тактов синхронизации для данной программы, деленным на частоту синхронизации.

Важной характеристикой, часто публикуемой в отчетах по процессорам, является среднее количество тактов синхронизации на одну команду - CPI (clock cycles per instruction). При известном количестве выполняемых команд в программе этот параметр позволяет быстро оценить время ЦП для данной программы.

Таким образом, производительность ЦП зависит от трех параметров: такта (или частоты) синхронизации, среднего количества тактов на команду и количества выполняемых команд. Невозможно изменить ни один из указанных параметров изолированно от другого. Поскольку базовые технологии, используемые для изменения каждого из этих параметров, взаимосвязаны: частота синхронизации определяется технологией аппаратных средств и функциональной организацией процессора; среднее количество тактов на команду зависит от функциональной организации и архитектуры системы команд; а количество выполняемых в программе команд опре