Интерфейсные управляющие выводы

FRAME# s/t/s Cycle Frame (циклический временной интервал) управляется текущим «управителем» для указания начала и продолжительности доступа. Пока FRAME# активен, идет передача данных

IRDY# s/t/s Initiator Ready (готовность инициализации) Во время записи, IRDY# показывает, что на линиях присутствуют достоверные данные. При чтении это показывает, что мастер готов к приему данных. Циклы ожидания вставляются до тех пор, пока активны IRDY# и TRDY#.

TRDY# s/t/s Target Ready (целевое устройство готово) показывает способность целевого агента (выбранного устройства) завершить текущую фазу данных транзакции. При чтении указывает, что на линиях AD присутствуют достоверные данные. Во время записи это означает готовность целевого устройства к принятию данных

STOP# s/t/s Stop показывает, что текущее подчиненное устройство посылает «управителю» запрос на останов текущей транзакции.

LOCK# s/t/s Lock показывает операцию, которой для завершения требуется множество транзакций. Целевое устройство, поддерживающее LOCK#, должно обеспечить исключение минимум 16 байтов (с учетом выравнивания). Для главных интерфейсов, находящихся после системной памяти, также необходимо выполнить LOCK#.

IDSEL входной Initialization Device Select (выбор устройства инициализации) используется для выбора кристалла при транзакциях чтения конфигурации и записи.

DEVSEL# s/t/s Когда активным выводом Device Select (выбор устройства) управляют, он показывает, что управляющее устройство дешифрировало данный адрес как цель текущего доступа. DEVSEL# в качестве входа показывает, было ли выбрано на шине какое-то устройство.

Арбитражные выводы (только для мастеров шины)

REQ# t/s Request (запрос) показывает арбитру, что данному агенту требуется поработать с шиной. Этот сигнал - типа «от одного пункта к другому». Каждый мастер имеет свой собственный вывод REQ#.

GNT# t/s Grant (разрешение) показывает агенту, что разрешен доступ к шине. Этот сигнал типа «от одного пункта к другому». Каждый мастер имеет свой собственный вывод GNT#.

Выводы для сообщения об ошибках требуются всем устройствам:

PERR# s/t/s Parity Error (ошибка контроля по четности) предназначен только для сообщения об ошибках контроля по четности во время всех транзакций PCI,

SERR# o/d System Error предназначен для выдачи сообщений об ошибках контроля по четности для адреса/.

Выводы прерывания (необязательно) используется выход с открытым коллектором PCI предусматривает одну линию прерываний для устройства с одной функцией INTA#,, и до четырех линий

прерывания - для многофункциональных устройств или соединителя.

INTA# o/d Interrupt A - для запроса прерывания.

INTB# INTC# INTD# o/d Interrupt B, C, D - для запроса прерывания для многофункциональных устройств.

Любая функция на многофункциональном устройстве может быть соединена с любой линией INTx#. Регистр вывода прерывания определяет, какая из линий INTx# используется для запроса прерывания. Поставщик системы свободен в выборе способа объединения различных сигналов INTx# из разъема PCI, для их соединения с контроллером прерываний. Они могут быть объединены по «ИЛИ», либо переключаться электроникой под управлением программы, либо как-то иначе, путем комбинации выше перечисленных способов.

Выводы поддержкиКЭШа (необязательно)

Кэшируемая память PCI должна реализовывать оба вывода поддержки кэширования в качестве входных, чтобы разрешить работу как с КЭШем сквозной записи, так и с КЭШем обратной записи. Если кэшируемая память размещена на PCI, то интерфейс, соединяющий кэш обратной записи и PCI, должен реализовывать оба вывода в качестве выходных; а интерфейс, соединяющий PCI и кэш сквозной записи, может реализовывать только один вывод.

SBO# вх/вых Snoop Backoff указывает удачную попытку для изменения состояния линии. Когда сигнал SBO# неактивный, и активен SDONE, то это означает успешный результат «вмешательства».

SDONE вх/вых Snoop Done указывает состояние «вмешательства» для текущего доступа. Когда сигнал неактивен, то это показывает, что результат «вмешательства» все еще ожидается. Когда сигнал активен, то это показывает, что «вмешательство» завершено.

Выводы расширения шины до 64-бит (необязательно)

AD[63::32] t/s Address и Data (адрес и данные) мультиплексированы. В течение фазы данных, когда активны REQ64# и ACK64#, передаются дополнительные 32 бита данных.

C/BE [7::4]# t/s Bus Command и Byte Enables (команды шины и разрешение байта) мультиплексированы на одних и тех же выводах. В течение фазы адреса (когда используются команды ЦАП и когда активен REQ64#) передается фактическая команда шины по линиям C/BE[7::4 В течение фазы данных показывают, какой байт содержит значимые данные, при условии, что активны оба сигнала REQ64# и ACK64#.

REQ64# s/t/s Когда Request 64-bit Transfer управляется текущим «управителем» шины, то он показывает, что тот желает передать данные, использую для пересылки 64 бита.

ACK64# s/t/s Когда Acknowledge 64-bit Transfer управляется устройством, которое успешно дешифрировало данный адрес в качестве агента текущего доступа, то он показывает, что агент желает передать данные, используя при этом 64 бита.

PAR64 t/s Parity Upper DWORD - это бит контроля по четности, который защищает линии AD[63::32] и C/BE[7::4]. PAR64 идет в течение одного такта после фазы начального адреса, когда активен REQ64, и по линии C/BE[3::0] поступает команда ЦАП. Также PAR64 идет в течение такта после второй фазы адреса команды ЦАП.

Выводы JTAG / периферийного сканирования (необязательно)

Стандарт IEEE 1149.1, Порт для тестирования и архитектура периферийного сканирования («Test Access

Port and Boundary Scan Architecture»), включен в качестве необязательного интерфейса для PCI устройств. Стандарт IEEE 1149.1 определяет правила и ограничения для проектирования ИС (интегральных схем) в соответствии с 1149.1. Включение в состав устройства порта для тестирования (TAP - Test Access Port) позволяет использовать периферийное сканирование для проверки устройства и платы, на которой данное устройство установлено. TAP состоит из четырех выводов (в общем случае - из пяти), которые используются для организации последовательного интерфейса с контроллером TAP внутри PCI- устройства. Поставщик системы ответственен за проектирование и функционирование в системе последовательных цепочек стандарта 1149.1 («кольца»). Обычно «кольцо» по стандарту 1149.1 создается путем соединения вывода TDO одного устройства с выводом TDO другого, чтобы получить последовательную цепочку устройств. В этом случае микросхемы получают одни и те же сигналы TCK, TMS и необязательные сигналы TMS#. Все кольца по стандарту 1149.1 соединены либо с тестирующим разъемом материнской платы для целей тестирования, либо к ИС резидентного контроллера по стандарту 1149.1. Спецификация PCI поддерживает платы расширения с разъемом, который предусматривает сигналы периферийного сканирования. Устройства на плате расширения можно соединять в цепочку на материнской плате.

TCK in Test Clock используется для синхронизации ввода собранной информации и данных в устройство и их вывода во время работы с TAP.

TDI in Test Data Input используется для последовательного ввода в устройство тестирующих данных и команд при работе с TAP.

TDO out Test Output используется для последовательного вывода тестирующих данных и команд из устройства при работе с TAP.

TMS out Test Mode Select используется для управления в устройстве состоянием контроллера TAP.

TRST# in Test Reset обеспечивает асинхронную инициализацию контроллера TAP. Этот сигнал по стандарту IEEE 1149.1 необязателен.

Методы соединения и использования системы колец по стандарту 1149.1 с платами расширения включают: Использование кольца по стандарту 1149.1 на плате расширения только во время тестирования этой

платы расширения на производстве. В этом случае, кольцо по стандарту 1149.1 на материнской плате не должно контактировать с сигналами по стандарту 1149.1 для плат расширения. Материнская плата должна самотестироваться непосредственно в ходе производства. Создание для каждой платы расширения в системе независимых колец, по стандарту 1149.1, на материнской плате. Например, если на плате есть два разъема расширения, то на материнской плате должны оставаться свободные кольца по стандарту 1149.1. Инициализацию ИС, которая допускает иерархичную многоточечную адресацию по стандарту 1149.1. Это позволит обрабатывать множество колец по стандарту 1149.1 и разрешит многоточечную адресацию и операции. Платы расширения, не поддерживающие стандарт интерфейса IEEE 1149.1, должны осуществлять переход от вывода TDI платы к выводу TDO.

Операции на шине Операции на шине показывают агенту тип транзакции, которая требуется мастеру. Эти операции кодируются в течение фазы адреса на линиях C/BE[3::0]#.

0000 Interrupt Acknowledge (подтверждение прерывания)

0001 Special Cycle (специальный цикл)

0010 I/O Read (чтение при вводе - выводе)

0011 I/O Write (запись при вводе - выводе)

0100 Зарезервировано

0101 Зарезервировано

0110 Memory Read (чтение памяти)

0111 Memory Write (запись в память)

1000 Зарезервировано

1001 Зарезервировано

1010 Configuration Read (чтение конфигурации)

1011 Configuration Write (запись конфигурации)

1100 Memory Read Multiple (множественное чтение памяти)

1101 Dual Address Cycle (двойной цикл адреса)

1110 Memory read Line (линия чтения памяти)

1111 Memory Write and Invalidate (запись в память и недействительные данные)

Команда Interrupt Acknowledge представляет собой неявное обращение к системному контроллеру прерываний. Биты адреса в течение фазы адреса не имеют логического значения и показывают длину

возвращаемого вектора.

Команда Special Cycle обеспечивает механизм передачи сообщений по шине PCI. Он используется для физических сигналов, когда необходимо организовать связь по sideband -сигналам.

Команда I/O Read I/O Write используется для чтения / передаче данных, агента, отображенного в адресном пространстве ввода - вывода. По линиям AD[31::00] поступает адрес байта. Должны дешифрироваться все 32 бита. Byte Enables указывает размер передачи, при этом он должен соответствовать адресу байта.

Команда Memory Read Memory Write используется для чтения передаче данных агента, отображенного в пространстве адресов памяти. Когда целевое устройство возвращает признак готовности, это подразумевает готовность данных.

Команда Configuration Read Configuration Write используется для чтения пространства конфигурации каждого агента передачи. Агент выбран, когда активен его сигнал IDSEL, и на линии AD[1::0] присутствует 00. Во время фазы адреса цикла или цикла конфигурации, AD[7::2] адресует одно из 64 двойных слов DWORD (и внутри каждого DWORD допускается адрес байта или байтов); конфигурации с информацией о каждом устройстве, а AD[31::11] - логически это не предусматривает. AD[10::08] показывает, что каждый элемент многофункционального агента адресован.

Команда Memory Read Multiple является семантически идентичной команде Memory Read, за исключением того, что в ней дополнительно указывается возможность выбора мастером более чем одной строки кэширования, перед отсоединением. Контроллер памяти должен продолжать конвейерную обработку памяти, пока активен сигнал FRAME#. Эта команда предназначена для работы по передаче больших последовательностей данных, когда можно повысить эффективность системы памяти (и запрашивающего мастера), при последовательном чтении дополнительной строкиКЭШа, когда программной установленный буфер доступен для временного хранения.

Команда Dual Address Cycle (DAC) используется для передачи 64-разрядного адреса в устройства, поддерживающие 64-битную адресацию. Те же устройства, которые поддерживают только 32-битную адресацию, должны обработать эту команду, как зарезервированную, и никогда не отвечать на текущую транзакцию.

Команда Memory read Line является семантически идентичной команде Memory Read, за исключением того, что в ней дополнительно указывается возможность завершения мастером более чем двух 32-битных фаз данных PCI. Эта команда предназначена для работы с большими последовательностями передаваемых данных, когда можно повысить производительность системы памяти (и запрашивающего мастера), при чтении строкиКЭШа до конца в случае, если время реакции на запрос менее одного цикла памяти. Как и в случае с командой Memory Read, буферы выборки должна быть отменены прежде, через данный путь доступа будут инициированы события синхронизации.

Команда Memory Write and Validate семантически идентична команде Memory Write, за исключением того, что она дополнительно гарантирует передачу как минимум одной полной строкиКЭШа; например, это требуется, когда мастеру необходимо записать все байты внутри адресованной строкиКЭШа за одну транзакцию PCI. Мастер может позволить транзакции «перейти» границу строкиКЭШа только в случае, если это предполагает передачу и всей последующей строки. Для выполнения этой команды требуется наличие у мастера регистра конфигурации, в котором был бы указан размер строкиКЭШа (за более подробной информацией обращайтесь к разделу 6.2.4). Это позволит повысить производительность памяти, путем отмены строки в КЭШе обратной записи, без осуществления фактического цикла обратной записи, и, таким образом, сокращая время доступа. Обращайтесь к разделу 3.3.3.1. за информацией относительно блокировок по времени обработки.

Командыс применением регистра длины строкиКЭШа:

Команда Memory Read - блочной передачи половины строкиКЭШа или менее.

Команда Memory Read Line блочной передачи от половины строкиКЭШа до трех строкКЭШа.

Команда Memory Read Multiple Используется при блочной передаче более трех строкКЭШа.

Основное использование команд без применения регистра длины строкиКЭШа:

Команда Memory Read Используется при блочной передаче, если имеется две и менее пересылок данных.

Команда Memory Read Line блочной передачи, если количество пересылок данных составляет от 3 до 12.

Команда Memory Multiple Read больших блоков данных (до 13 и более пересылок).

Блок состоит из фазы адреса и одной или более фаз данных. PCI поддерживает передачу блоками как для адресного пространства памяти, так и для адресного пространства ввода - вывода.

Значение всех сигналов проверяется по фронту синхроимпульса

FRAME# Управляется мастером для того, чтобы он мог указать начало и конец транзакции.

IRDY# Управляется мастером, чтобы он мог инициировать циклы ожидания.

TRDY# Управляется целевым устройством, чтобы оно могло инициировать циклы ожидания.

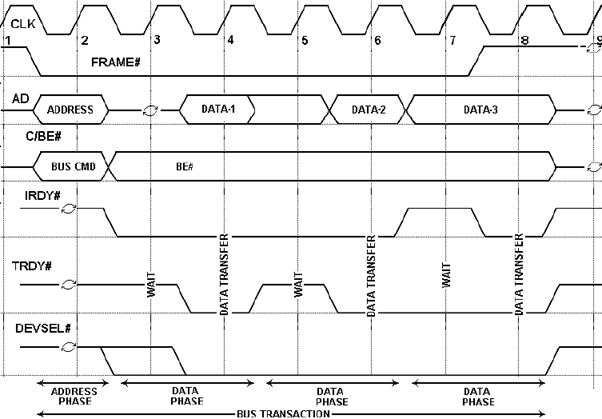

Линии AD[1::0] используются и для генерирования сигнала DEVSEL#, указывающего при передаче последний допустимый байт При использовании команд для работы с памятью, AD[1::0] принимает следующие значения: AD1 AD0 Режим в блоке: 0 - Линейное приращение; 1 - Режим переключения строкиКЭШа (порядок заполненияКЭШа - как у Intel486 /Pentium./и т.д.) X - Зарезервировано (разрыв связи после первой фазы данных). Транзакция чтения начинается фазой адреса, которая происходит во 2-ом такте, когда устанавливается сигнал FRAME#. В течение фазы адреса AD[31::00] содержит адрес, а C/BE[3::0]# - команду шины. Такт 3 является первым тактом для первой фазы данных. В течение фазы данных C/BE# показывает, какие линии передачи байта участвуют в текущей фазе данных. Фаза может состоять из циклов передачи и ожидания. При транзакции чтения первой фазе данных требуется оборотный цикл (инициированный целевым устройством через сигнал TRDY#). В этом случае адрес будет достоверен во 2-ом такте, а затем мастер завершит управление адресными линиями. Самый ранний такт, в котором целевое устройство может гарантировать достоверные данные - это такт 4. Целевое устройство должно управлять адресными линиями после оборотного цикла, когда установлен сигнал DEVSEL#.

Рис. 4.2. Базовая операция чтения

Фаза данных завершается, когда данные перемещены, при этом сигналы IRDY# и TRDY# установлены на фронте синхроимпульса

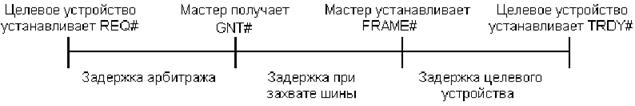

Временные задержки на PCI

Рис. 4.3. Составляющие задержки

Для быстрых устройств передача транзакции составит T+8 тактов. (T - число в пакете) Шина PCI работает на частоте 33 МГц.

Время задержки при ожидании первых данных составляет 16 тактов (0.5 мкс) для всех устройств, которые не являются шинами расширения.

Время между последовательностями фаз данных при блочной передаче - восемь тактов.

Побайтовый доступ на шине расширения занимает 1.5 мкс, причем время задержки первых данных равно 6 мкс при 32-битном доступе через интерфейс шины расширения.

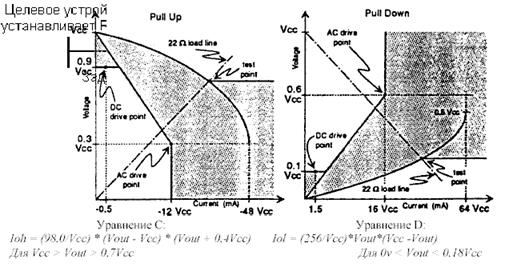

Рис.4.4. ВАХ для 3.3-вольтовой среды передачи сигналов

Электрическая спецификация– уровни, времена, последовательности нагрузка:

Максимальный допустимый перекос синхронизации - 2ns.

Все PCI-разъёмы имеют четыре шины питания: +5V,+ 3.3V, + 12V, и -12V. Дорожки сигнала должны также оставаться полностью над плоскостью 3.3В или полностью над 5-вольтовой плоскостью.

Сигналы, которые должны переходить из одной области в другую должны быть разведены на противоположных сторонах платы так, чтобы они находились в плоскости, которая не расчленяется. Если это не возможно и сигналы должны быть направлены над зазором, два слоя должны быть связаны вместе ёмкостью 0.01microF (5-вольтовая плоскость с 3.3-вольтовой) быстродействующими конденсаторами

для каждых четырех сигналов, пересекающих зазор, и конденсатор располагается не далее 0.25 дюйма от точки пересечения сигналов с зазором.

1. Максимальные длины дорожек для всех сигналов 32-разрядного интерфейса ограничены 1.5 дюймами для 64-битовых плат и 32-разрядных плат.

2. Длины дорожек дополнительных сигналов, используемых для 64 разрядного расширения ограничены до 2-х дюймов на всех 64 разрядных платах.

3. Длина дорожки для CLK сигнала равна 2.5 дюйма плюс/минус 0.1 дюйма для 64- разрядных плат и 32-разрядных плат и они должны быть направлены только к одной нагрузке. Конечные автоматы используют три типа переменных; состояния, PCI сигналы и внутренние сигналы.

State in a state machine = STATE PCI signal = SIGNAL

Internal signal = Signal

Уравнения конечного автомата принимают логическую операцию, где "*" является функцией AND и имеет старшинство над "+", который является функцией OR. Круглые скобки имеют старшинство над

обоими. Символ "!" используется для отрицания (NOT) переменных. В уравнениях конечного автомата,

PCI SIGNAL's представляют фактическое состояние сигнала на PCI шине. Истинные сигналы низкого уровня будут истинны или установлены, когда они появляются как !SIGNAL# и ложны или сняты, когда

они появляются как SIGNAL#. Истинные сигналы высокого уровня будут истинны или установлены, когда они появляются как SIGNAL и ложны или сняты, когда они появляются как !SIGNAL. Внутренние

сигналы будут истинны,

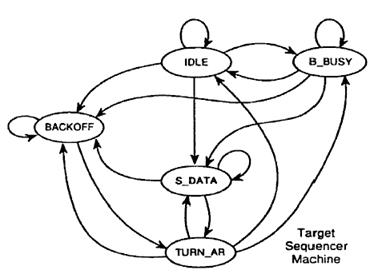

Рис.4.5. Граф конечного автомата шины

IDLE или TURN_AR условие неактивности или завершенная транзакция на шине

goto IDLE if FRAME#

goto B_BUSY if !FRAME# * !Hit

goto S_DATA if !FRAME# * Hit * (!Term + Term * Ready) * (FREE + LOCKED * LOCK#)

goto BACKOFF if !FRAME# * Hit * (Term * !Ready + LOCKED * !LOCK#)

B_BUSY - Не включается в текущую транзакцию.

goto B_BUSY if (!FRAME# + !IRDY#) * !Hit

goto IDLE if FRAME#

goto S_DATA if (!FRAME# + !IRDY#) * Hit* (!Term + Term * Ready) * (FREE + LOCKED * L_lock#)

goto BACKOFF if (!FRAME# + !IRDY#) * Hit *(Term * !Ready + LOCKED * L_lock#)

S_DATA - Агент принял запрос и ответит.

goto S_DATA if !FRAME# * !STOP# * !TRDY# * IRDY#+ !FRAME# * STOP# + FRAME# * TRDY# * STOP#

goto BACKOFF if !FRAME# * !STOP# * (TRDY# +!IRDY#)

goto TURN_AR if FRAME# * (!TRDY# + !STOP#)

BACKOFF - Агент занят и неспособен ответить в это время.

goto BACKOFF if !FRAME#

goto TURN_AR if FRAME#

agent объект, который функционирует на шине компьютера.

master агент, который инициализирует транзакцию шины.

NMI немаскируемое прерывание.

phase один или больше временных периодов, в которых передается один блок информации, состоящий из: адреса и данных.

Последовательные линии

В 16-ти разрядных архитектурах компьютеров существовала шина внешних устройств EISA, которая перешла и архитектуру компьютеров на базе процессоров Pentium. Параллельные магистрали обладают высоким быстродействием, но они дороги и требуют большого объема аппаратных затрат. В последовательных шинах данные передаются по одной или двум линиям (+ синхросигнал). Последовательные шины по своей тактовой частоте превосходят параллельные, тем более, что сигналы в них все более аналоговые, двуполярные. Однако необходимость передачи служебной «шапки» (это может быть и сотня бит) не дает выигрыша по быстродействию. Для снижения влияния служебной информации на скорость обмена стремятся к пакетной передачи данных.

На замену шин EISA и в некотором роде PCI пришли шины USB 1.0 и Fire Wire (стандарт IEEE 1394). Ориентация 1394 - первоначально жесткий диск и видео периферийные устройства, которые могут потребовать ширину полосы частот шины сверх 100 Mbs (резерв спецификации до 800 Mbs.). Протокол поддерживает как синхронный, так и асинхронные передачи тем же комплектом четырех сигнальных проводов (две дифференциальных пары сигналов - синхронизации и данных).

По своей структуре они схожи. Обе передают питание, частоты разнятся на несколько десятков. У последней, как указано, два сигнала, синхросигнал переключается лишь тогда, когда передаваемый бит данных не меняются. Но во многом они схожи.

Шина USB (USB1.1., USB2.0.., USB3.0.) является примером «короткой» линии и пришла, в определенной степени, на смену шине EISA.

Универсальная последовательная шина USB - внешний интерфейс ввода/вывода - это несомненное достижение в архитектуре ПК. Последовательные порты типа RS-232 обеспечивают скорость от 9.6Kbps до 115.2Kbps в зависимости от микросхемой логики асинхронного приемопередатчика UART (Universal Asynchronous Recive/Transmitter). Максимальная пропускная способность USB 1.1. составляет 12Mbps, хотя фактически скорость передачи данных ближе к 8Mbps, включая 1Mbps-подканал для медленных устройств типа мышь и клавиатура. Этого вполне достаточно, чтобы обслужить потребности всех устройств от мыши до видеомагнитофонов, ISDN-адаптеров и сжатого видео MPEG. Использование низкоскоростных устройств позволяет перераспределить полосы частот и выделить больше пропускной способности тем устройствам, которые в этом нуждаются.

Достоинством USB являются как асинхронные, так и изосинхронные порты. Изосинхронные передачи видео и аудио данных имеют приоритет, гарантируя непрерывность потоков данных для приложений реального времени. USB позволяет включать до 127 устройств, связанных в звездообразную технологию: каждое устройство может содержать в себе USB-концентратор, к которому можно подсоединить дополнительные устройства.

Индустриальным стандартом контроллеров USB считается комплект Intel One-Stop-Shopping серий i8X930Ax/i8Х930Hx/i8X931Ax/i8X931Hx монтажа 64pin PQFP (Plastic Quad Flat Package), предназначенные для построения USB-концентраторов, USB-оконечных устройств и для изготовления USB-контроллеров для монитора.

Хотя USB медленнее, имея пропускную способность 12Mbps (1.5MBps), чем SCSI (замена последней последовательная шина ATA 3 – 600 Мбайт/с), она предлагает высокоскоростные и Plug-and-Play возможности для такой периферии, в которой традиционно используются последовательный, параллельный или специальный порт, например, клавиатура, мышь или монитор. USB также подходит для небольших периферийных устройств типа сканеров, в которых ранее применялись специализированные адаптеры или SCSI-контроллеры. Для периферии, не использующей SCSI-контроллеры, USB предлагает оборудование примерно в сто раз более быстрое, чем, например, традиционные последовательные порты с максимальной скоростью передачи 115Kbps. Параллельные порты со скоростью обмена 2Mbps работают примерно в шесть раз медленнее, чем USB. Вдобавок, один USB-порт может обслуживать до 126 периферийных устройств без каких-либо дополнительных компьютерных ресурсов, таких как IRQ. Сегодняшние последовательные или параллельные, порты для клавиатуры или монитора обычно могут обслужить только одно устройство. Более того, мало потребляющий USB-контроллер обеспечивает электропитание всех устройств, подключенных к его шине, уменьшив тем самым количество розеток на стене либо распределительных щитков (однако устройства, потребляющие относительно много энергии, такие как сканеры, нуждаются в дополнительных розетках).

USB также предоставляет так называемый режим hot swapping - возможность подсоединять и переключать внешние устройства без выключения компьютера. Такие устройства, как клавиатура или мышь с двухсторонним обменом, не могут сегодня переключаться в режиме hot swapping. USB-контроллер имеет один стандартный кабель для любых периферийных устройств, что обеспечивает легкость подключения и снижение стоимости систем. Если устройства поддерживают PnP, то необходимые драйверы устройств могут автоматически загружаться и выгружаться.

Топология шины USB представляет собой управляющий блок USB, концентраторы, кабели и функциональные устройства. Существует только один управляющий блок в любой системе USB. Интерфейсом для связи с ПК является управляющий контроллер, который может быть реализован в комбинации с аппаратными или аппаратно-программными средствами. Встроенный в управляющий блок корневой концентратор обеспечивает одну или несколько точек подключения.

Концентраторы - ключевой элемент в архитектуре PnP USB. Они представляют собой устройства, которые обеспечивают многочисленные подключения к USB. Точки подключения именуются портами. Каждый концентратор превращает одну точку подключения в несколько. Данная архитектура поддерживает сочленение нескольких концентраторов.

Рис.4.6. Пирамида концентраторов шины, вид 1

Рис.4.6. Пирамида концентраторов шины, вид 2

Входной порт концентратора подсоединяет его к управляющему блоку. Каждый из выходных портов концентратора позволяет подключение к другому концентратору или функциональному блоку. Концентраторы могут определять подсоединение или отключение на каждом выходном порте и позволяют распределить энергию по выходным устройствам, а так же устанавливать оптимальную скорость для устройства, подключенного к выходному порту. Здесь показано, как можно объединить функциональные устройства и повысить возможность системы. Устройство, содержащее концентратор и одно или несколько функциональных устройств, именуется комбинированным устройством.

Рис.4.6. Пирамида концентраторов компьютера

USB передает сигналы и электропитание по 4-х-жильному кабелю, который состоит из сегментов длиною не более 5 метров. Длина кабельного сегмента USB меняется в зависимости от сопротивления проводника, мощности устройства и гибкости кабеля. Сигналы передаются по двум проводам кабеля D+ и D- (DATA+ и DATA-), которые имеют волновое сопротивление Z=90. Провода Vbas (+5VDC) и GND предназначены для электропитания устройств (питание и земля соответственно). Номинальное напряжение для Vbas составляет +5V. Чтобы гарантировать оптимальную величину сигнала на входе и необходимое сопротивление, на каждом конце кабеля применяются оконечные устройства. Оконечные устройства также позволяют фиксировать подсоединение и отсоединение на каждом порту и различать высоко- и низкоскоростные устройства.

Рис.4.6. Кабель USB

В USB 1 существует 2 режима передачи сигнала. Высокоскоростная передача сигнала составляет 12Mbps. Низкоскоростной режим обеспечивает скорость 1.5Mbps и более сильную защиту от электромагнитных помех. Оба режима могут поддерживаться одновременно, в одной и той же системе USB в режиме переключения между передачами данных. Высокоскоростной режим необходим для работы с быстрыми устройствами IHVs (Independent Hardware Vendors), DVPDs (Digital Video Peripheral Devices), VCRs (Video Cassette Recorders), ISDN-периферией, принтерами, сканерами и т.д. Режим низкой скорости необходим для поддержки ограниченного числа устройств с узкой полосой пропускания, такими, как joystick, mouse, keyboard.

Все транзакции в шине могут включать в себя до 3 пакетов. Каждая транзакция начинается, когда управляющий контроллер посылает маркерный пакет (Token Packet) USB, описывающий тип и направление транзакции, адрес устройства и номер конечной точки. В данной транзакции данные передаются либо от управляющего блока к устройству, либо наоборот. Источник транзакции затем посылает пакет данных, или сигнализирует об отсутствии данных для передачи. Получатель, в общем случае, отвечает пакетом квитирования (HandShake Packet), который подтверждает передачу данных.

Данные в USB передаются по каналам. Существует 2 типа каналов: поток и сообщение. Потоковые данные не имеют определенной USB-структуры, в то время как у сообщений она есть. Кроме того, каналы связаны с полосой пропускания данных, типом передачи данных и характеристиками конечной точки, такими, как направленность и размер буфера. Каналы начинают свое существование, когда конфигурируется USB-структура. Только канал управления 0 существует всегда, как только устройство включено, для того, чтобы установить доступ к конфигурации устройства, статусу и управляющей информации.

Использование транзакций позволяет управлять потоками в каналах. На аппаратном уровне это предохраняет буферы от ситуации неполного завершения или перезагрузки с помощью NACK-квитирования, которое управляет скоростью данных. Механизм управления потоками позволяет создавать гибкие расписания, которые адаптируют параллельную обработку к смеси потоков данных разных типов. Так, многочисленные каналы с разнотипными данными обслуживаются за разные интервалы времени и с пакетами разных размеров. Сама же архитектура USB поддерживает 4 основные типа передачи данных:

Передачи управления. Они используются программным обеспечением USB для конфигурирования устройств, когда они впервые подсоединены. Отдельный драйвер может выбрать специфическое управление для обеспечения передачи данных без потерь.

Групповая пересылка. Обычно состоит из больших объемов данных, которые используются принтерами, сканерами или цифровыми камерами. Групповые данные - это последовательные данные, надежный обмен которых обеспечивается на уровне аппаратуры путем обнаружения ошибок в технических средствах и дополнительно активизирует перезагрузку ПК. Полоса пропускания, которую занимают групповые данные, должна быть доступна в любой момент времени и не занимается другими типами данных.

Передача прерываний. Небольшая порция данных, переданных в произвольный момент времени от периферийного устройства, называется прерыванием. Такие данные могут быть посланы устройством в любое время и передаются USB со скоростью, не меньшей, чем определено устройством. Прерывания обычно состоят из уведомления о событии, символов и адреса, которые организованы как 1 байт или более. Прерывания используются для поддержки низкоскоростных устройств протокола USB 1.5Mbps.

Изохронные передачи. Изохронные данные (непрерывные данные) создаются, передаются и используются в реальном времени. Согласованная по времени информация подразумевает устойчивую скорость, при которой изохронные данные принимаются и передаются. Изохронные данные должны доставляться с необходимой скоростью, чтобы сохранить согласование по времени, так как изохронные данные могут быть чувствительны к задержкам доставки. Изосинхронная порция представляет собой непрерывный поток и используется для передачи звука или видео. К передаче изосинхронных данных предъявляются очень высокие требования.

Типичный пример изохронных данных - аудио- или видеосигналы. Если скорость передачи этих потоков данных не сохраняется, то происходит нарушение синхронизации и получается искаженное восприятие. Даже если данные переданы с соответствующей скоростью, задержки в работе буферов могут вызвать искажения в протоколах типа Т.120 (аудиоконференции).

Потоки изохронных данных USB сосредоточены в определенной части полосы пропускания, чтобы обеспечить доставку данных с необходимой скоростью. USB сконструирована таким образом, чтобы максимально уменьшить задержку передачи изохронных данных.

USB выделяет полосу пропускания каналам в том случае, когда соединение произошло. Полоса пропускания распределяется среди каналов в соответствии со спецификой работы. Устройствам USB требуется буфер, и предполагается, что чем большую полосу пропускания занимает устройство, тем большего размера ему требуется буфер. Целью архитектуры USB является обеспечение времени обращения к буферу в пределах нескольких миллисекунд.

Полоса пропускания может распределяться по потокам данных, в результате чего достаточно широкий диапазон устройств может подключиться к шине USB. Распределение полосы пропускания в USB - блокирующее, то есть если размещение дополнительного канала ограничивает работу уже существующей полосы пропускания, дальнейшее назначение каналов будет отменено или блокировано. Когда канал закрыт, выделенная для него полоса пропускания освобождается и может быть переназначена на другой канал.

Процесс USB превращает физическую топологию в индивидуальные отношения между ПО клиента (находящимся в функциональном блоке) и функциональными устройствами. Этот процесс включает в себя операции согласования и конфигурации, и находится под контролем ПО управляющего блока USB, спрятанного в верхнем слое (ПО клиента). ПО клиента запрашивает службы USB о передаче данных в систему программного обеспечения (ПО USB).

Настройка вновь подсоединенных устройств не требует участия пользователя. В тоже время, поддержка USB изохронных передач превращает ПК в мощное средство коммуникации.

Для периферийных устройств серийно выпускается USB-контроллер 82930A, выполненный на базе микроконтроллера архитектуры MCS-251, который поддерживает как скоростные каналы со скоростью передачи 12Mbps, так и каналы со скоростью 1.5Mbps, синхронную, изосинхронную передачу данных и режимы управления мощностью, необходимые для устройств USB. Эти контроллеры разработаны для периферийных устройств, подключаемых к компьютеру.

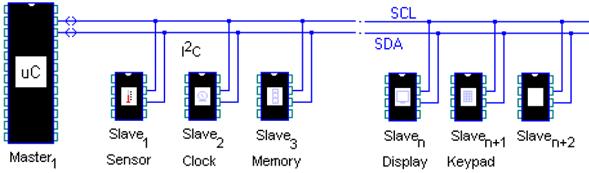

Рис.4.7. Соединение модулей с I2C

Последовательные шины передачи данных присутствуют и в микроконтроллерных структурах. Их число составляет несколько десятков. Отдельные из них получили боьшое распространение и стали стандартом, поддерживаемым многими производителями микросхем.

Одина из них - промышленная шина I2C. Длина ее может быть близка к километру. Частота могут достигать 5 МГц.Подключение модулей без учета обязательных резисторов подброса показана на рис. 4.7.

Архитектура потоков команд

Архитектура последовательной машины базируется на выборке команд по указателю команд. Это определяет точку обработки в потоке команд.

Однако присутствует несколько механизмов (подпрограмм, прерываний, переключения задач), поддерживаемых аппаратно процессорами, позволяющих запустить в обработку несколько потоков команд. Рассмотрим их на примере архитектуры микроконтроллера и одного из них - механизма прерываний.

Как правило, каждое устройство микроконтроллера представляет собой сложный блок. Однако оно отображается регистровой моделью. Через установку разрядов запускаются макросы внутренних микропрограммных автоматов. Примером может служить модель контроллера прерываний (Interrupt Controller).

Рис. 5.1. Регистры контроллера прерываний

Примечание: 1. Младшие 16 битов адреса. 2. Только очистка флагов.

Разряды регистров обычно содержат указания на режимы работы, команды или данные, например, разряды системного управляющего регистра контроллера прерываний (SYSCR) задают режимы работы блока (рис. 5.3).

Рис. 5.2. Вектора системных прерываний

Детальное рассмотрение процесса обработки прерываний, показывает ощутимую потерю производительности. Множество процессоров и не коррелированные потоки команд позволяют исполнять их на много процессорных архитектурах.

Рис. 5.3. Назначение разрядов регистра SYSCR контроллера прерываний