Архитектура HyperTransport

Архитектура системной платы

По мере «взросления» компьютеров постоянно расширяются функции чипсета системной платы и изменяются подходы к его построению. В задачу чипсетов для 80286/386 входили увязка шины процессора с относительно несложным контроллером памяти и подключение к этой связке шины (E)ISA, на которой располагались все устройства. Постепенно стала усложняться подсистема памяти — появился кэш на системной плате, а потом к нему добавился встроенный кэш процессора. Для процессоров класса 486 производительности шины (E)ISA оказалось уже недостаточно, и появились новые шины. Шина VLB, как просто физически оформленная разъемом системная шина процессора класса 486, особых хлопот чипсету не доставляла. Однако появилась шина PCI, для которой пришлось строить мост от системной шины. Поначалу ее называли «пристроечной» (mezzanine bus), но вскоре она надолго стала центральной шиной, вокруг которой компоновались все остальные элементы. Ее центральное место не оспаривалось, поскольку шина PC имела высокую производительность — 132 Мбайт/с. Традиционно на схемах шину PCI изображают посередине, как экватор. Процессор и память (вместе с кэш-памятью) напротивВдладислав Кубарев изображают выше — «севернее», а шину ISA и все устройства, подключаемые к PCI и ISA, изображают ниже — «южнее экватора». Соответствующие части чипсета получили укоренившиеся названия северных (north) и южных (south). Созвучное слово «серверный» относится к чипсету, ориентированному на применение в компьютерах-серверах.

Архитектура системной платы прошла путь от шинно-мостовой к хабовой, особняком держится архитектура HyperTransport. Независимо от архитектуры системной платы и физической реализации соединений все современные периферийные устройства (или контроллеры и адаптеры их интерфейсов) представляются логическими устройствами (точнее, функциями). Стандартный набор атрибутов PCI (конфигурационным пространством со стандартными заголовками) обеспечивает удобный единый интерфейс конфигурирования устройств (распределения системных ресурсов). Этот интерфейс поддерживается и в PCI-X, и в PCI-E; он учитывается и в HyperTransport. Традиционные (legacy) устройства (PIC 8259A, DMA 8237A, СОМ - и LPT-порты и другие аксессуары PC) в плане конфигурирования держатся особняком — их конфигурация является статической и не меняется на протяжении более двух десятков лет.

Шинно-мостовая архитектура

В шинно-мостовой архитектуре имеется центральная магистральная шина, к которой остальные компоненты подключаются через мосты. В роли центральной магистрали сначала выступала шина (E)ISA, затем ее сменила шина PCI. Шинно-мостовая архитектура чипсетов просуществовала долгое время и пережила много поколений процессоров (от 2-го до 7-го). Перемещение вторичного кэша с системной платы на процессор (Р6 и Pentium 4 у Intel и К7 у AMD) несколько упростило северную часть чипсета — в ней не надо управлять статической кэш-памятью, а остается лишь обеспечивать когерентность процессорного кэша с основной памятью, доступ к которой возможен и со стороны шины PCI.

Шина PCI в роли главной магистрали удержалась недолго: видеокартам с ЗD-акселератором ее пропускной способности, разделяемой между всеми устройствами, оказалось недостаточно. Тогда и появился порт AGP как выделенный мощный интерфейс между графическим акселератором и памятью (а также процессором).

203-204

При этом задачи северного моста усложнились: контроллеру памяти приходится работать уже на три фронта — ему посылают запросы процессор, мастера шины PCI (и ISA, но тоже через PCI) и порт AGP. Пропускная способность AGP в режиме 2х/4х/8х составляет 533/1066/2133 Мбайт/с, так что шина PCI по производительности стала уже второстепенной. Однако в шинно-мостовой архитектуре она сохраняет свою роль магистрали подключения всех периферийных устройств (кроме графических). В качестве мощного представителя шинно-мостовой архитектуры можно рассматривать чипсет AMD-760. Здесь имеются первичная шина PCI на 64 бит и 66 МГц, являющаяся «экватором», и вторичная шина для подключения рядовой периферии.

Шина, к которой подключается множество устройств, является узким местом по ряду причин. Во-первых, из-за большого числа устройств, подключенных (электрически) к шине, не удается поднять тактовую частоту до уровня, достижимого в двухточечных соединениях. Во-вторых, шина, к которой подключается множество разнотипных устройств (особенно расположенных на картах расширения), обременена грузом обратной совместимости со старыми периферийными устройствами. Например, предусмотренные возможности повышения производительности PCI используются не всегда: расширение разрядности до 64 бит обходится слишком дорого (большое число проводников порождает свои проблемы), а повышение частоты до 66 МГц для шины возможно лишь если все ее абоненты поддерживают эту частоту. Достаточно установить одну «простую» карту PCI, и производительность центральной шины падает до начальных 133 Мбайт/с. То же можно сказать и о PCI-X: достаточно подключить к ней одно устаревшее устройство PCI, и все протокольные усовершенствования будут отменены.

Хабовая архитектура

С введением высокоскоростных режимов UltraDMA (ATA/66, ATA/100, а затем и AT А/133) связь двухканального контроллера IDE с памятью через шину PCI стала слишком сильно нагружать эту шину. Кроме того, появились высокоскоростные интерфейсы Gigabit Ethernet, FireWire (100/200/400/800 Мбит/с) и USB 2.0 (480 Мбит/с). Ответом на эти изменения в расстановке сил стал переход на хабовую архитектуру чипсета. В данном контексте хабы — это специализированные микросхемы, обеспечивающие передачу данных между своими внешними интерфейсами. Этими интерфейсами являются «прикладные» интерфейсы подключения процессоров, модулей памяти, шин расширения и периферийные интерфейсы (ATA, SATA, USB, FireWire, Ethernet). Поскольку к одной микросхеме все эти интерфейсы не подключить (слишком сложна структура и много требуется выводов), чипсет строится, как правило, из пары основных хабов (северного и южного), связанных между собой высокопроизводительным каналом.

203-204.

Северный хаб чипсета выполняет те же функции, что и северный мост шинно-мостовой архитектуры: он связывает шины процессора, памяти и порта AGP. Однако на южной стороне этого хаба находится уже не шина PCI, а высокопроизводительный интерфейс связи с южным хабом. Пропускная способность этого интерфейса составляет 266 Мбайт/с и выше, в зависимости от чипсета. Если чипсет имеет интегрированную графику, то в северный хаб входит и графический контроллер со всеми своими интерфейсами (аналоговыми и цифровыми интерфейсами дисплея, шиной локальной памяти). Чипсеты с интегрированным графическим контроллером могут иметь внешний порт AGP, который становится доступным при отключении встроенного графического контроллера. Есть чипсеты, у которых порт AGP является чисто внутренним средством соединения встроенного контроллера, и внешний графический контроллер к ним может подключаться только по шине PCI.

С появлением PCI-E архитектура не слишком изменилась: северный хаб (мост) вместо порта AGP теперь предлагает высокопроизводительный (8х или 16х) порт, а то и пару портов PCI-E для подключения графического адаптера. Маломощные (1х) порты PCI-E могут предоставляться как северным, так и южным хабами (это решает разработчик чипсета). В последнем случае корневой комплекс PCI-E «расползается» по двум микросхемам чипсета, связанным между собой «фирменным» интерфейсом. Использования PCI-E как единой коммуникационной базы внутри чипсета пока не наблюдается.

Архитектура HyperTransport

Технология (архитектура) HyperTransport (HT) задумывалась как альтернатива шинно-мостовой архитектуре системных плат. Технология разработана компаниями AMD, Apple Computers, Broadcom, Cisco Systems, NVIDIA, PMC-Sierra, SGI, SiPackets, Sun Microsystems, Transmeta. Первый релиз вышел в 2001 году, в 2003-м — версия 1.10. Прежнее кодовое название — LDT (Lighting Data Transport).

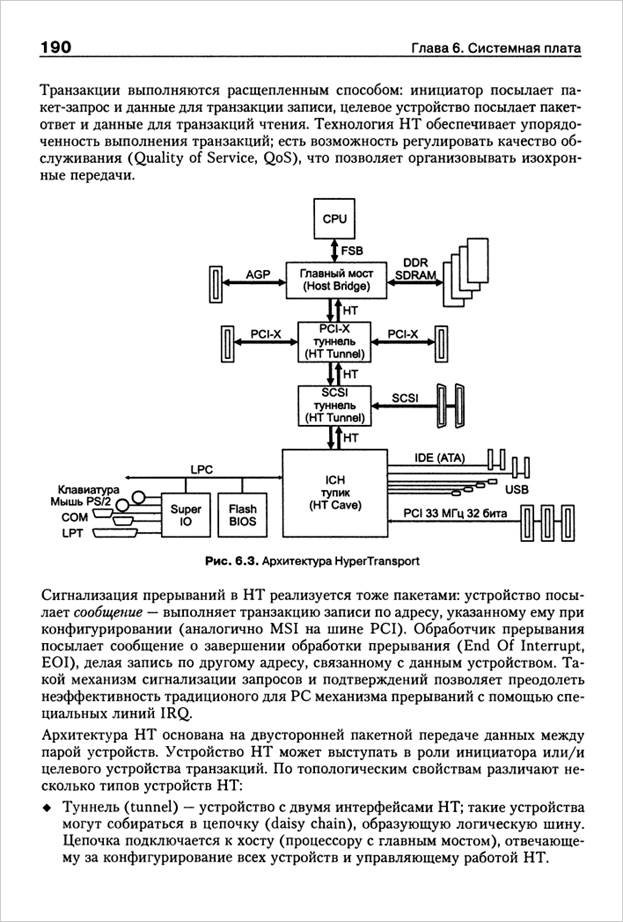

Основная идея НТ — замена шинного соединения компонентов (периферийных устройств) системой двухточечных встречно направленных соединений. При этом достижима более высокая тактовая частота интерфейсов, что обеспечивает их более высокую (по сравнению с шиной) пропускную способность. Главный мост (host bridge) обеспечивает связь НТ с ядром — процессором и памятью. Периферийные контроллеры, требующие высокой пропускной способности, реализуются в виде НТ-туннелей. В архитектуре предусматривается и мостовая связь с шиной PCI.

Архитектура НТ обеспечивает все типы транзакций процессоров и устройств PCI, PCI-X и AGP, используемые в PC. Транзакции выполняются в виде серий передач пакетов различных типов. В традиционных транзакциях целевое устройство идентифицируется адресом: чтение и запись в пространстве памяти, ввод-вывод в конфигурационном пространстве, а также считывание вектора прерывания из PIC 8259A и специальные циклы PCI. Для унификации транзакций все пространства отображаются на единое 40-битное пространство адресов (объем 1 Тбайт), адрес передается в управляющих пакетах. Первые 1012 Гбайт пространства выделены для отображения обычного пространства памяти (для ОЗУ и ввода-вывода, отображенного на память). В оставшейся 12-гигабайтной области размещаются конфигурационное пространство (32 Мбайт), пространство ввода-вывода (32 Мбайт), память SMM, пространства адресов для выдачи векторов и подтверждения прерываний; 54 Мбайт остались в резерве. Транзакции НТ обеспечивают программное взаимодействие процессора с устройствами, прямой доступ к памяти и одноранговое взаимодействие устройств с адресацией в описанном комбинированном пространстве. Существует сетевое расширение спецификации, поддерживающее обмен сообщениями (как в сетях), причем возможны и широковещательные сообщения.

Транзакции выполняются расщепленным способом: инициатор посылает пакет-запрос и данные для транзакции записи, целевое устройство посылает пакет-ответ и данные для транзакций чтения. Технология НТ обеспечивает упорядоченность выполнения транзакций; есть возможность регулировать качество обслуживания (Quality of Service, QoS), что позволяет организовывать изохронные передачи.

Сигнализация прерываний в НТ реализуется тоже пакетами: устройство посылает сообщение — выполняет транзакцию записи по адресу, указанному ему при конфигурировании (аналогично MSI на шине PCI). Обработчик прерывания посылает сообщение о завершении обработки прерывания (End Of Interrupt, EOI), делая запись по другому адресу, связанному с данным устройством. Такой механизм сигнализации запросов и подтверждений позволяет преодолеть неэффективность традиционого для PC механизма прерываний с помощью специальных линий IRQ.

Архитектура НТ основана на двусторонней пакетной передаче данных между парой устройств. Устройство НТ может выступать в роли инициатора или/и целевого устройства транзакций. По топологическим свойствам различают несколько типов устройств НТ:

· Туннель (tunnel) — устройство с двумя интерфейсами НТ; такие устройства могут собираться в цепочку (daisy chain), образующую логическую шину. Цепочка подключается к хосту (процессору с главным мостом), отвечающему за конфигурирование всех устройств и управляющему работой НТ.

· Мост (bridge) — устройство, соединяющее одну логически первичную шину (подключенную к хосту) с одной или несколькими логически вторичными шинами (цепочками). Мост имеет набор регистров, информация которых позволяет управлять распространением транзакций между этими шинами (аналогично мосту PCI).

· Коммутатор (switch) — устройство с несколькими интерефейсами НТ, по структуре аналогичное нескольким мостам PCI, подключенным к одной (внутренней) шине.

· Тупик, или пещера (cave) — устройство с одним интерфейсом НТ.

Хост (host) — это «хозяин шины», подключающийся к ней через главный мост и выполняющий функции конфигурирования (аналогично и совместимо с PCI). Основной вариант топологии — цепочка устройств-туннелей, подключенная верхним концом к хосту. Каждый интерфейс НТ состоит из двух независимых частей: передатчика и приемника. Каждому устройству при конфигурировании выделяются свои области в адресном пространстве. В цепочке устройства-туннели транслируют пакеты сверху вниз (нисходящий трафик) и снизу вверх (восходящий). Если в нисходящем управляющем пакете устройство обнаруживает свой адрес, оно «понимает», что обращаются к нему, и принимает соответствующую информацию (управляющие пакеты и данные). Восходящий трафик туннель транслирует «вслепую». На полученные запросы устройство отвечает посылкой пакетов вверх, включая их в транслируемый восходящий трафик. Таким образом обеспечивается программное взаимодействие процессора с устройствами. Собственные запросы на доступ к памяти устройство посылает тоже вверх, как и запросы (обращения) к другим устройствам (независимо от положения целевого устройства — выше или ниже в цепочке). Доставку пакета адресату обеспечивает главный мост: он разворачивает пакет, принятый из цепочки (адресованный не к ОЗУ), и посылает его вниз — так организуется одноранговое взаимодействие. На пакет, адресованный к ОЗУ, главный мост организует ответ от контроллера памяти, реализуя таким образом прямой доступ к памяти.

Возможны и более сложные топологии, например дерево (с мостами), позволяющее подключать больше тупиковых устройств. Возможна и цепочка с двумя хостами (на обоих концах), которая может использоваться двояко. В первом варианте обеспечиваются избыточность (дублирование функций хоста) и разделяемость узлов (доступность обоим хостам). При этом один главный мост становится ведущим («настоящим», разворачивающим одноранговые запросы и ответы), через него обеспечивается конфигурирование узлов. Другой мост становится ведомым — он является лишь средством связи второго хоста (процессора) с узлами. Программно при конфигурировании (инициализации НТ) роли мостов можно поменять. Во втором варианте одно из устройств разбивает шину (перестает работать туннелем), в результате получаются два хоста со своими короткими цепочками собственных (неразделяемых) устройств. С применением коммутаторов можно строить и более сложные, но беспетлевые топологии.

Технология HyperTransport предназначена для соединения компонентов компьютеров и коммуникационной аппаратуры, но только в пределах платы — слоты и карты расширения технологией НТ не рассматриваются. Для передачи информации используются два встречных однонаправленных набора высокоскоростных сигналов:

· CAD[n:0] — шина управления (control), адреса (address) и данных (data) разрядностью 2, 4, 8, 16 или 32 бита, причем во встречных направлениях может использоваться различная разрядность. У передатчика сигналы CADOUTx, у приемника — CADINx;

· CTL — сигнал-признак, позволяющий различать передачи пакетов управляющей информации и данных. У передатчика сигнал CTL0UT, у приемника — CTLIN;

· CLK — сигнал синхронизации (по фронту и спаду), для каждого байта CAD используется своя линия CLK (их может быть 1, 2 или 4). У передатчика сигналы CLKOUTx, у приемника — CLKINx.

Сигналы передаются по дифференциальным парам проводов с импедансом 100 Ом, сигналы — LVDS (низковольтные дифференциальные, уровень1,2 В). Частота синхронизации 200, 300, 400, 500, 600, 800 и даже 1000 МГц обеспечивает физическую скорость передачи 400, 600, 800, 1000, 1200, 1600 и 2000 МТ/с (миллионов передач в секунду), что при самых больших разрядности (32 бит) и частоте обеспечивает пиковую скорость передачи данных до 8 Гбайт/с. В первой версии предельная частота была 800 МГц, что давало скорость 6,4 Гбайт/с. Поскольку пакеты могут передаваться одновременно в обоих направлениях, можно говорить о суммарной пропускной способности 12,8 или 16 Гбайт/с.

Помимо сигналов для передачи пакетов, имеются сигналы сброса и инициализации (PWR0K — признак стабильности питания и синхронизации, RESET# — сброс цепочки устройств), а также управления энергопотреблением (LDTST0P# — разрешение/запрет использования соединения при смене состояний системы, LDTREQ# — индикатор активности соединения или его запроса устройством). Эти сигналы «медленные», их формируют передатчики с открытым стоком (open-drain), все одноименные сигналы цепочки объединяются, выполняя функцию «монтажного ИЛИ». Уровни сигналов — LVTTL/CMOS (2,4 В).

По замыслу разработчиков, НТ должна стать архитектурой построения PC, однако пока что используется лишь технология НТ. В вышеприведенном примере главный мост реализует интерфейс AGP. В 64-битных процессорах AMD, в которых применяется НТ, главный мост размещается в самом процессоре. При этом у процессора оказывается два интерфейса: интерфейс памяти (пока что DDR SDRAM) и НТ в качестве системной шины. В распространенных чипсетах (от VIA, SiS) к интерфейсу НТ подключается только северный хаб, обеспечивающий лишь интерфейс подключения графического адаптера — AGP или PCI-E. Южный хаб соединяется с северным собственным интерфейсом, так что использования НТ как универсальной транспортной структуры для множества компонентов пока не наблюдается.

Северные мосты и хабы

Северный хаб (как и мост) определяет основные возможности системной платы:

· Поддерживаемые процессоры — типы, частоты системной шины, возможности мультипроцессорных или избыточных конфигураций. Типы процессоров определяются протоколами системной шины, которых в настоящее время несколько:

· шина Pentium процессоров для сокета 7, Super7 (и сокета 5); частоты 50-100 МГц;

· шина Р6 процессоров для сокета 8, слотов 1 и 2, сокета-370; частоты 66-133 МГц;

· шина Pentium 4 для сокетов с 423, 478/479, 603/604 и 775 контактами; частота синхронизации 100-266 МГц при 4-кратной «накачке» обеспечивает частоту передачи данных 400-1066 МГц;

· шина EV-6 процессоров Athlon, Duron, Semptron для слота А и сокета А (462 контакта); частоты передачи данных 200-400 МГц (тактовая частота в два раза ниже);

· интерфейс HyperTransport процессоров со встроенным контроллером памяти (Athlon 64, Opteron, мобильные Turion 64 и Semptron) для сокетов с 754 и 939/940 выводами.

· Типы памяти и частота работы шины памяти:

· DRAM (FPM, EDO, BEDO) с временем доступа 50-80 нс;

· SDRAM (PC66, РС100, РС133) с частотами 66-133 МГц;

· DDR SDRAM (РС1600, РС2100, РС2700, РС3200) с частотами 100-200 МГц (частота передачи в два раза выше);

· DDR2 SDRAM (РС2-3200, РС2-4300, РС2-5300, РС2-5300, РС2-6400) с частотами 200-400 МГц (частота передачи в два раза выше);

· RDRAM (РС600, РС700, РС800, РС1066) с частотами 300, 356, 400 и 533 МГц.

· Максимальный объем памяти. На него влияет ряд факторов:

· число слотов под модули памяти и поддерживаемые объемы модулей (допустимое число устанавливаемых модулей при работе на самой высокой частоте шины памяти может оказаться меньше, чем число слотов);

· максимальное количество «рядов» микросхем памяти (может ограничивать возможное число устанавливаемых двусторонних модулей).

· Число каналов памяти — пока чаще один, но для повышения пропускной способности применяются два канала. Поначалу двухканальность использовалась только для RDRAM (здесь меньше интерфейсных сигналов в канале), теперь есть двухканальные контроллеры DDR SDRAM и DDR2 SDRAM. В оба канала должны быть установлены попарно однотипные модули (как раньше пары SIMM-72 для Pentium).

· Возможность и эффективность применения разнородной памяти (например, DRAM вместе с SDRAM в старых платах, SDRAM и DDR SDRAM в более новых) и модулей с разным быстродействием (разная латентность при одинаковой частоте). В ряде случаев разнородная память снижает производительность всей памяти, и не всегда эта потеря окупается получаемым увеличением объема ОЗУ.

· Для старых плат с DRAM — возможность чередования банков (у современных типов памяти чередование банков внутреннее).

· Поддержка контроля достоверности памяти и исправления ошибок (ЕСС).

· Средства подключения графического акселератора (высокопроизводительное подключение), для которого уже имеется несколько вариантов:

· порт AGP и его характеристики (режим 2х/4х/8х, внеполосная адресация SBA, быстрая запись Fast Writes); для чипсетов с интегрированной графикой интересна доступность порта при отключении внутреннего графического адаптера;

· слоты PCI-E 8х или 16х для подключения графического адаптера (1 или 2 порта); слоты PCI-E 1х может обеспечивать как северный, так и южный хаб;

· графический адаптер с интерфейсом HyperTransport (пока что это теоретический вариант).

· Возможности системы управления энергопотреблением ACPI или АРМ) - реализуемые энергосберегающие режимы процессора и памяти, управление производительностью, SMM.

Северный мост плат для сокетов 5, 7 и Super7 определяет также политику записи кэша, применяемые типы и быстродействие микросхем статической памяти, возможный размер кэша и кэшируемой области основной памяти. Для современных плат без кэша все эти параметры определяются процессором, а политику обратной записи поддерживают уже все платы.

Северный мост определяет также поддерживаемые частоты и разрядность шины PCI и PCI-X, возможное количество контроллеров шины PCI (число пар сигналов арбитра PCI), способы буферизации, возможности одновременных обменов. Северный хаб на эти параметры уже не влияет, поскольку шины PCI и PCI-X подключаются к южному хабу.

Южные мосты и хабы

Южный хаб чипсета обеспечивает подключение шин PCI, PCI-X и «маломощных» портов PCI-E, ISA (но уже не всегда), АТА (2 канала), SATA, USB, FireWire, а также «мелких» контроллеров ввода-вывода, памяти CMOS и флэш-памяти с системным модулем BIOS. В южной части располагаются таймер (8254), контроллер прерываний (совместимый с парой 8259 или APIC), контроллер DMA для шины ISA и периферии системной платы. Если в чипсет интегрирован звук, то южный хаб (мост) имеет контроллер интерфейса AC-Link или HDA Link для подключения аудиокодека, а то и сам аудиокодек. Поскольку шина ISA отправляется в отставку, для контроллеров ввода-вывода, ранее подключавшихся к шине X-BUS (это практически та же ISA), ввели новый интерфейс LPC (Low Pin Count). Он, как и следует из названия, имеет малое число линий [6], что значительно облегчает разработку чипсета и системной платы. Флэш-память для хранения системной памяти BIOS стали помещать в специальный хаб (firmware hub), соединяемый с южным хабом отдельной шиной (аналогичной LPC). Флэш-память может подключаться и прямо к шине LPC. Для подключения энергонезависимой памяти (EEPROM) хаб может иметь дополнительный последовательный интерфейс. Для обслуживания процессоров, имеющих дополнительную сервисную шину SMBus, а также для поддержки слота CNR хаб может иметь последовательный интерфейс I2C (Inter 1С — интерфейс связи микросхем). Этот же интерфейс может использоваться для чтения идентификаторов модулей памяти. В южный хаб интегрированных чипсетов вводят и контроллер локальной сети (как правило, Ethernet).

Логически южный хаб представляется как набор виртуальных мостов и устройств, подключенных к главной шине PCI. Однако обмены данными с широкополосными устройствами (IDE, SATA, USB, FireWire, Ethernet, AC'97 или HDA) на внешнюю шину PCI все-таки не «выплескивают», иначе теряется смысл южного хаба.

Южный хаб (или мост) определяет перечисленные далее параметры системной платы:

· Параметры шины PCI (только для хабов):

· версия интерфейса и режимы (PCI, PCI-X, PCI-X 2.0);

· разрядность (32 или 64 бита);

· частота (33 или 66 МГц для PCI, до 133 МГц для PCI-X);

· допустимое количество контроллеров шины (число каналов арбитра, которое влияет на число слотов и встроенных устройств PCI).

· Число маломощных (4х) портов PCI-E.

· Параметры интерфейсов AT А:

· поддерживаемые режимы UltraDMA — ATA/33, ATA/66, ATA/100, АТА/133;

· независимость каналов — электрическое разделение каналов, возможность одновременной работы двух каналов.

· Параметры интерфейса SAT А: тип контроллера (желательно AHCI), число портов, возможность одновременного использования с параллельной шиной.

· Число портов и версия шины USB.

· Наличие интерфейса AC-Link или HDA Link.

· Наличие шины ISA.

· Возможность эмуляции DMA на шине PCI (PC-PCI, DDMA).

· Возможности мониторинга состояния:

· число каналов измерения питающих напряжений;

· число каналов измерения температуры;

· число каналов измерения частоты вращения вентиляторов.

Контроллеры гибких дисков, интерфейсных портов, клавиатуры, CMOS RTC могут входить в собственно чипсет, а могут быть реализованы и на отдельных «инородных» микросхемах. От них зависят следующие параметры системной платы:

· наличие порта PS/2 Mouse (есть во всех платах АТХ);

· режимы параллельного порта (стандартный, двунаправленный, ЕСР, ЕРР, поддержка FIFO и DMA);

· режимы последовательных портов (стандартом считается совместимость с 16550А и поддержка FIFO и DMA);

· поддержка IrDA;

· типы поддерживаемых дисководов (2,88 Мбайт поддерживают теперь почти все контроллеры, но эта возможность не востребована дисководами и дискетами).