Раздел 1. Информационные технологии управления безопасностью

ISBN 978-985-488-895-8.

Пособие содержит краткие теоретические сведения, методическиеуказания к выполнению лабораторных занятий.Пособие разработано для магистрантов специальности 1-59 81 01 «Управление безопасностью производственных процесов», а также будет полезно для магистрантов других специальностей. Практические задания предназначены для магистрантов и преподавателей, владеющих теоретическим материалом по темам предлагаемых практических работ.

УДК 331.45(076.5)

ББК 65. 247я73

ISBN 978-985-48-8.© Силков Н.И.,ЧеремисиновД.И.,Мельникова Е.М., 2014

© УО «Белорусский государственный

университет информатики

и радиоэлектроники», 2014

СОДЕРЖАНИЕ

| Введение | ||

| Раздел 1. Информационные технологии управления безопасностью…………… | 4 | |

| Тема 1. | Изучение элементов систем безопасности…………………………….. | |

| Тема 2. | ИзучениеVHDL-моделей систем………………………………………. | |

| Тема 3. | Изучение входных-выходных сигналов систем безопасности……….. | |

| Тема 4. | Изучение потокового стиля описания………………………………….. | |

| Тема 5. | Изучение процессов в дискретном устройстве………………………... | |

| Тема 6. | Изучение вычислителяVHDL………………………………………….. | |

| Раздел 2. Электронные системы безопасности……………………...................... | 26 | |

| Тема 7. | Изучение триггерных схем…………………………………………….. | |

| Тема 8. | Изучениедвоичных счетчиков…………………………………………. | |

| Тема 9. | Изучение сумматоров…………………………………………………… | |

| Тема 10. | Изучение активных фильтров………………………………………….. | |

| Тема 11. | Изучениепреобразователей сигналов…………………………………. |

Введение

В промышленности используется достаточно большая номенклатура производственных процессов и технологического оборудования, отличающихся функциональной сложностью, способом использования изготовления, методамиобеспечения безопасности труда и др. показателями. Процесс управления безопасностью производственных процессов не может быть выполнен без знаний инновационных технологий, современных компьютерных технологий, функционирования узлов и электронных блоков систем безопасности.

В пособии представлена тематика занятий, нацеленная на выполнение работы по изучению электронных схем, предназначенных для решенияисследовательских и практических задач создания систем безопасности. Пособие поможет магистрантам в практическом освоении методики расчётов основных вариантованалоговых и дискретных схем, алгоритмов, и элементной базы,обеспечивающих функционирование информационных систем безопасности,приобретения практических навыков использования операционных усилителей для выполнения математических операций, связанных с применением и разработкой систем безопасности. Разработка может быть использована для проверки уровня знаний при самостоятельной подготовке к занятиям. По дисциплинам«Информационные технологии управления безопасностью»и «Электронные системы безопасности» в пособии предусмотрено по 8 тем для практических занятий.

Раздел 1. Информационные технологии управления безопасностью

Тема 1. Изучение элементов систем безопасности

Цель:исследование структур и устройств, реализуемых в схемотехнике КМОП. Изучение основ построения логических элементов различных типов, сравнение их преимуществ и недостатков.

Теоретические сведения

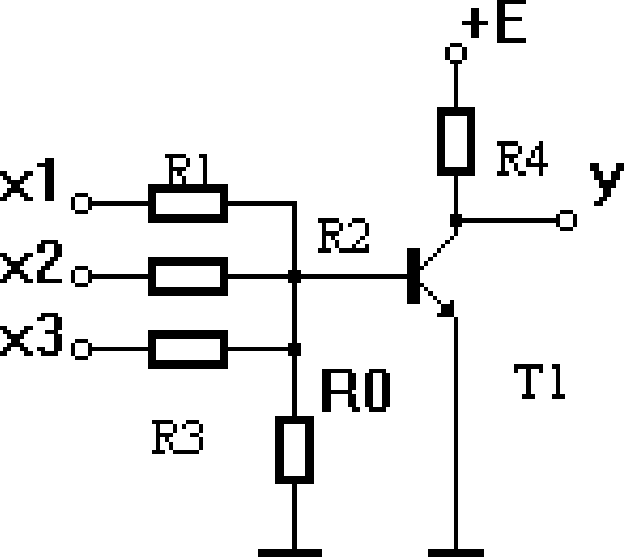

Логические элементы РТЛ– типа относительно простотыв реализации на технологическом уровне.Они позволяют выполнять интегральные схемы (ИС) малой степени интеграции. На рис. 1.1 показана электрическая схема и таблица истинностиРТЛ-элемента, выполняющего логическую функцию 3ИЛИ-НЕ.

| Значения входных сигналов | Значение выхода | ||

|  |  | у |

а)

б)

Рис. 1.1 – Электрическая схема (а)и таблица истинности (б) РТЛ – элемента 3ИЛИ-НЕ

В схеме используется биполярный транзистор n-p-n типа, который работает в ключевом режиме. В исходном состоянии, когда входной сигнал на всех контактах Х1, Х2, Х3 равен логическому нулю (лог.«0»), потенциал базы близок к нулевому значению и отсутствуют базовый и коллекторный токи транзистора Т1. Следовательно, транзистор Т1 находится в закрытом состоянии (транзисторный ключ разомкнут). На выходе элемента «Y» в этом случае устанавливается высокий потенциал, близкий к потенциалу источника питания «+Е», что соответствует лог. «1» на выходе.

Если на любой из входов элемента подать лог. «1», то базовый ток транзистора увеличится, потечет коллекторный ток и транзистор откроется, потенциал коллектора будет близок к нулевому значению (транзисторный ключ замкнут). На выходе «Y» логического элемента появится низкий потенциал -лог. «0».

Таким образом, лог. «1» на любом из трех входов инвертируется элементом в лог. «0» на выходе, что соответствует логической операции 3ИЛИ-НЕТ.

Недостатки РТЛ-элементов:

- низкая технологичность из-за необходимости применения высокостабильных резисторов;

- высокая потребляемая мощность;

- малые коэффициенты разветвления и объединения;

- низкая нагрузочная способность;

относительно низкое быстродействие из-за насыщенного режима работы транзистора, высоких постоянных времени входных цепей и высокого выходного сопротивления.

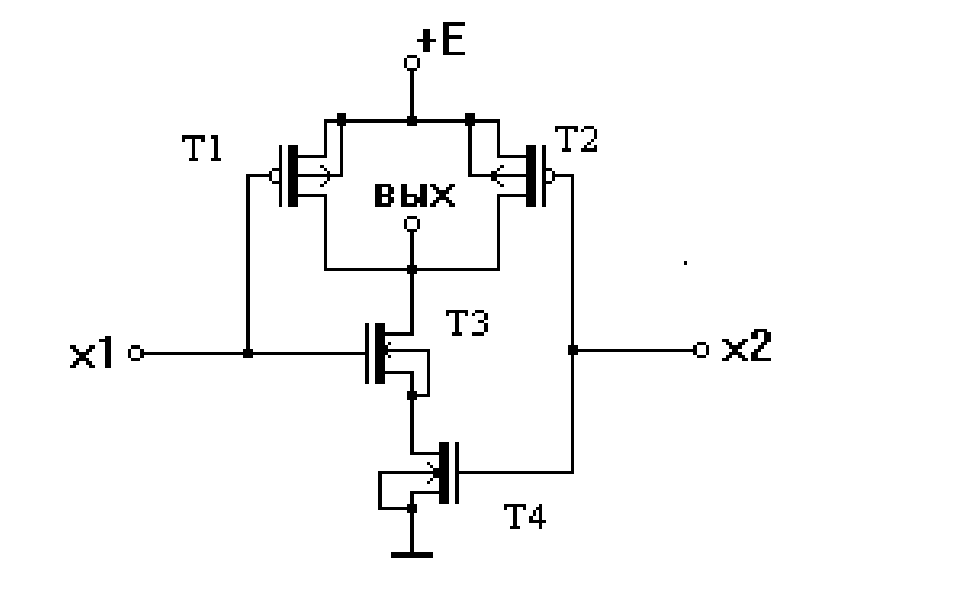

Логические элементы КМОП (CMOS) – типа. Комплементарные элементы типа КМОП (CMOS) строятся по технологии «металл-окись-полупроводник». Схема элемента КМОП типа И-НЕ показана на рис.1.1. Обычно элементы строятся только на МОП – транзисторах с разным, взаимодополняющим (комплементарным) типом проводимости – на транзисторах с индуцированными n-каналами (Т3, Т4) и p-каналами (Т1, Т2).

Рассмотрим принцип действия КМОП – элемента. Пусть, например, в исходном состоянии на обоих входах присутствует лог. «0». В этом случае верхние транзисторы Т1 и Т2 будут открыты, а нижние транзисторы Т3, Т4 будут закрыты. На выходе будет установлена лог. «1», но ток в микросхеме протекать не будет из-за закрытых транзисторов Т3, Т4.

Если теперь на входе Х1 элемента (рис.1.1) изменить состояние с лог. «1» на лог. «0», а на входе Х2 – оставить лог. «1», то транзисторы Т1, Т4 откроются, а транзисторы Т2, Т3 – закроются. Смена входных сигналов приводит лишь к смене состояний Т1, Т4 и Т2, Т3, но состояние лог. «1» на выходе не меняется и ток после переключения также не течет. Аналогичная ситуация будет с элементом при лог. «1» на входе Х1 и лог. «0» на входе Х2 (только транзисторы Т1, Т4 закроются, а Т1, Т4 откроются).

| Значения входных сигналов | Значение выхода | |

|  | у |

а) б)

Рис.1.2 –Электрическая схема (а) и таблица истинности (б) логического элемента КМОП-типа 2И-НЕ на транзисторах с индуцированными каналами n (T3, T4)- и p (T1, T2)-типа

Однако одновременная подача на оба входа лог. «1» приводит к открытому состоянию Т3, Т4 и к закрытому состоянию Т1, Т2, при этом на выходе устанавливается лог. «0», но и в этом состоянии ток в схеме также не проходит.

Следовательно, в КМОП-элементе энергия потребляется только лишь во время переключений, т.е. в моменты смены состояний элемента из лог. «1» в лог. «0» и наоборот. Потребляемая элементом энергия зависит от частоты переключений и расходуется в основном на перезаряд емкостей нагрузки, паразитных емкостей монтажа и выводов элемента, а также межэлектродных внутренних емкостей транзисторов.

Таким образом, КМОП- элементы обладают самыми лучшими показателями по потребляемой мощности из всех типов логических элементов.

КМОП-элементы имеют высокую помехозащищенность и являются высокотехнологичными, так как не содержат в своих схемах разнородных элементов, таких как резисторы, диоды и т.п. Высокая плотность размещения элементов на единицу площади кристалла также свойственна этим элементам.

К недостаткам КМОП - элементов можно отнести:

- сравнительно низкое быстродействие относительно ТТЛ-элементов;

- низкая устойчивость к статическому электричеству, поэтому внутри элементов предусматриваются защитные диоды, изготавливаемые в едином технологическом цикле;

- паразитное влияние p-n-p и n-p-n– переходов, которые возникают в кристалле как побочные переходы в КМОП структурах, размещаемых на одном кремниевом кристалле. Эти паразитные биполярные структуры иногда отрицательно оказываются на поведении КМОП – элементов, вызывая так называемый тиристорный эффект, искажающий передаточную характеристику элемента.

Задание для самостоятельной работы

1) Составить таблицу истинности для элемента 3ИЛИ-НЕ на КМОП-транзисторах.

2) Составить функциональную схему логического элемента по заданному варианту таблицы истинности.

| A | B | C | D | Варианты заданий | |||||||||||||||

| X | |||||||||||||||||||

| X | X | X | |||||||||||||||||

| X | |||||||||||||||||||

| X | X | ||||||||||||||||||

| X | |||||||||||||||||||

| X | X | ||||||||||||||||||

| X | X | ||||||||||||||||||

| X | |||||||||||||||||||

| X | X | X | |||||||||||||||||

| X | X | ||||||||||||||||||

| X | |||||||||||||||||||

| X | |||||||||||||||||||

| X | |||||||||||||||||||

| X | X | X | |||||||||||||||||

| X | X | ||||||||||||||||||

| X | X |

Теоретические сведения

Граф – это конечное множество вершин и ребер, соединяющих их, т. е.:

G = (V,E),

где V – конечное непустое множество вершин; Е – множество ребер (пар вершин).

Если пары Е (ребра) имеют направление, то граф называется ориентированным (орграф), если иначе - неориентированный (неорграф). Если в пары Е входят только различные вершины, то в графе нет петель. Если ребро графа имеет вес, то граф называется взвешенным. Степень вершины графа равна числу ребер, входящих и выходящих из нее (инцидентных ей). Неорграф называется связным, если существует путь из каждой вершины в любую другую.

Обозначим количество вершин как n = ¦ V¦, а количество ребер как m = ¦ E ¦.

Графы в памяти могут представляться различным способом. Один из видов представления графов – это матрица смежности B(n*n); В этой матрице элемент b[i,j]=1, если ребро, связывающее вершины Vi и Vj существует и b[i,j]=0, если ребра нет. У неориентированных графов матрица смежности всегда симметрична.

Во многих случаях удобнее представлять граф в виде так называемого списка пар. Список пар содержит для каждой вершины из множества вершин V список тех вершин, которые непосредственно связаны с этой вершиной.

Граф G = (V,E) называется двудольным графом (биграфом), если множество V его вершин допускает разбиение на 2 непересекающихся подмножества V1 и V2 (две доли). Причем каждое ребро графа соединяет вершины из различных долей. Обозначается через G = (V1,V2,E) – двудольный граф с долями V1 и V2.

Моделью структурного описания является двудольный граф, одной долей которого являются порты (выводы) экземпляров элементов и порты самого устройства, а второй долей – цепи, соединяющие порты. Обозначения выводов экземпляров элементов предваряются его именем, показанным на рис. 2.1 в прямоугольнике фигуры. Экземпляры показаны прямоугольниками (не являются элементами графа), вершинами графа являются выводы экземпляра в прямоугольнике. Вершины цепей показаны кружками. Обозначения (имена) выводов и некоторых цепей для упрощения рисунка опущены.

Рис. 2.1 – Неориентированный двудольный граф структуры цифрового устройства

Задание для самостоятельной работы

В заданной логической схеме (рис. 2.1):

1) Отметить (назвать) цепи и элементы;

2) Построить список цепей (netlist) в виде списка пар двудольного графа схемы. Для примера на рис. 2.1 этот список имеет вид:

(N1: a, x.IN1, y.IN1)

(N2: b, x.IN2, y.IN2)

(N3: x.OUT, z.IN1)

(N4: y.OUT, z.IN2)

(N5: z.OUT, c)

3)Для схемы на рис. 2.2 нарисовать двудольный граф, одна доля которого – это цепи, вторая – контакты.

Рис. 2.2 – Электрическая схема

сети элементов

Теоретические сведения.

Комбинационные схемы – это схемы, у которых выходные сигналы

Y = (у1, у2,..., уm) в любой момент дискретного времени однозначно определяются совокупностью входных сигналов Х = (х1, х2..., хп), поступающих в тот же момент времени t. Реализуемый в КС способ обработки информации называется комбинационным потому, что результат обработки зависит только от комбинации входных сигналов и формируется сразу же при поступлении входных сигналов. Поэтому одним из достоинств комбинационных схем является их высокое быстродействие. Преобразование информации однозначно описывается логическими функциями вида Y = f(X). Значение функции различно для разных комбинаций входных переменных и может быть задано с помощью специальной таблицы – Таблицы истинности.

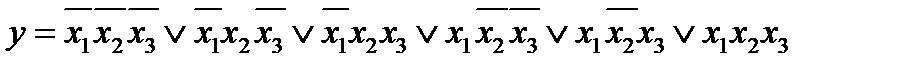

В левой части этой таблицы перечислены всевозможные комбинации входных переменных (наборы значений), а в правой - возможные реакции выходных сигналов.По данной таблице нетрудно составить аналитическое выражение (зависимость) для функции. Для этого наборы переменных, на которых функция принимает значение единицы, записываются как конъюнкции (логическое умножение) и связываются знаками логического сложения. Такие формы функций получили название дизъюнктивных нормальных форм (ДНФ). Если в этих функциях конъюнкции содержат все без исключения переменные в прямом или инверсном значении, то такая форма функций называется совершенной.

Алгебра логики устанавливает правила формирования логически полного базиса простейших функций, из которых могут строиться любые более сложные. Наиболее привычным базисом является набор трех функций {инверсия – [ , дизъюнкция - v, конъюнкция - л или &}.Работа с функциями, представленными в этом базисе, очень похожа на использование операций обычной алгебры.

Алгебра логики устанавливает, что существуют и другие комбинации простейших логических функций, обладающих свойством логической полноты. Например, наборы логических функций {инверсия, дизъюнкция} и {инверсия, конъюнкция} также являются логически полными. Наиболее интересны минимальные базисы, включающие по одной операции «отрицание дизъюнкции» –Стрелка Пирса и «отрицание конъюнкции» –штрих Шеффера.

Логическое выражение функции, получаемое на основе Таблицы истинности в виде совершенной дизьюнктивной формы, может быть упрощено путем его минимизации.

Таблица истинности функции Y=f(x1, x2, x3)

| x1 | x2 | x3 | Y |

По данным таблицы запишем аналитическое выражение:

Рис.3.1 – Структурная схема полусумматора (а) и обозначение полусумматора (б)

Задание для самостоятельной работы:

По логической схеме рис 3.1:

1) построить алгебраическое представление функций S и P;

2) построить таблицы истинности функций S и P;

3)построить алгебраическое представление реализуемых функций

по заданной комбинационной схеме.

Теоретические сведения.

Электрические сигналы играют ключевую роль в действии электронных элементов. Фактически трудно вообразить прибор, который не посылает или не получает некоторые сигналы. По этой причине сигналы – наиболее существенные объекты любого электронного прибора. В языке VHDL сигналы играют важную роль в описании связи между узлами или блоками. В отличие от переменных в классических языках программирования VHDL-сигналы содержат информацию о прошлых, настоящих и будущих значениях. Эта информация называется историей сигнала. Она позволяет проводить анализ временных зависимостей внутри VHDL системы.

Описание объекта проекта на языке VHDL имеет типовую структуру и содержит две части:

объявление объекта (entitydeclaration) и

определение архитектуры (architecturedefinition)

В декларативной части (entitydeclaration) описывают связи объекта с внешним миром – входы и выходы объекта. Это, прежде всего, спецификация интерфейса описываемого объекта. В описании архитектуры (architecturedefinition) определяют функцию (поведение) либоструктуруобъекта. Рис.4.1 иллюстрируетэтотпринцип.

Рис. 4.1 – Графический вид структуры объекта проекта

В текстовом файле на языке VHDLобъявление объекта (entitydeclaration) и определение архитектуры (architecturedefinition) разделены, как это показано на рис. 4.2.

Рис. 4.2 – Общий вид файла программы на языке VHDL

Объявление объекта в языке VHDL можно считать «оболочкой» архитектуры, скрывающей детали того, что находится внутри, но обеспечивающей «зацепки» для других модулей, использующих данный модуль. Эта идея служит основой иерархического подхода к проектированию систем: архитектура верхнего уровня может использовать (или «обрабатывать») другие объекты, оставляя архитектурные детали объектов нижнего уровня скрытыми от объектов более высокого уровня.

В табл. 4.1 представлен синтаксис объявления объекта. Целью объявления объекта, помимо присвоения объекту имени, является определение сигналов внешнего интерфейса или портов (ports) в части объявления объекта, которая называется объявлением портов (portdeclaration).

Табл. 4.1 –Синтаксис объявления объекта на языке VHDL

entityentity-name is

port(signal-names : mode signal-type;

signal-names : mode signal-type;

. . .

signal-names : mode signal-type);

endentity-name;

Обратите внимание, что после заключительного signal-type нет точки с запятой; изменение порядка следования закрывающей скобки и точки с запятой после нее - типичная синтаксическая ошибка программиста, начинающего писать на языке VHDL.

Кроме ключевых слов entity, is, port и end, объявление объекта содержит следующие элементы:

| entity-name | выбираемоепользователемимяобъекта; | |

| signal-names | список выбираемых пользователем имен сигналов внешнего интерфейса, состоящий из одного имени или из большего числа имен, разделенных запятой; | |

| Mode | одно из четырех зарезервированных слов, определяющих направление передачи сигнала: | |

| in | сигналнавходеобъекта; | |

| out | сигнал на выходе объекта; заметьте, что значение такого сигнала нельзя «прочитать» внутри структуры объекта; он доступен только объектам, использующим данный объект; | |

| buffer | сигнал на выходе объекта; в отличие от сигнала out его значение можно читать также внутри структуры данного объекта; | |

| inout | сигнал, который может быть входным или выходным для данного объекта; обычно этот режим используется применительно к входам/выходам схем с тремя состояниями; | |

| signal-type | встроенный или определенный пользователем тип сигнала. |

Каждому сигналу (а также переменной и константе) в программе на языке VHDL необходимо поставить в соответствие тип (type). Типом определяется множество или диапазон значений, которые может принимать данный элемент, и обычно имеется набор операторов (таких как сложение, логическое ИЛИ и т.д.), связываемых с данным типом.

Поскольку язык VHDL используется для представления аппаратных проектов в самых разных вариантах, средства типизации данных приобретают здесь особо важное значение. Например, они дают разработчику возможность представить группу проводников шины в виде:

- массивабитов,

- целогочисла.

В языке VHDL есть несколько предопределенных типов (predefinedtypes), которые поддерживают программы синтеза;они перечислены в табл. 4.2. В дальнейшем в пособии будут использованы только следующие предопределенные типы: bit, bit_vector и integer.

Табл. 4.2 – Предопределенные синтезируемые типы данных языка VHDL

bitboolean character

bit_vector integer

О правилах записи программы. Как и в других языках программирования, в языке VHDL пробелы и переходы с одной строки на другую в общем случае игнорируются, и для удобства чтения их можно вставлять как угодно.Комментарии начинаются с двух дефисов (--)и заканчиваются концом строки. В языке VHDL определено много специальных строк символов, называемых зарезервированными словами или ключевыми словами. В приведенном примере имеется несколько ключевых слов: entity, port, is, in, out, to, downto, range, end.Здесь и далее зарезервированные слова выделяются жирным шрифтом.Определяемые пользователем идентификаторы начинаются с буквы и содержат буквы, цифры и подчеркивания. Символ подчеркивания не может следовать за другим символом подчеркивания и не может быть последним символом идентификатора. В данном примере идентификаторами являются MUU_125, R, CLK, KOP, SNO, F, Y, P, CS, SKO, TPO. Зарезервированные слова и идентификаторы не чувствительны к регистру.

В языке VHDL под описанием архитектуры понимают описание функционирования специфицируемого объекта. Если декларативная часть описания объекта определяет его внешнее представление, задает интерфейсную спецификацию объекта, вводит имя объекта и входы/выходы ("порты", в терминах VHDL), то описание архитектуры задает его содержательное наполнение, спецификацию функциональной и временной работы описываемого объекта.

Внутренняя работа объекта задается его определением архитектуры (architecturedefinition), синтаксис которого в общем случае имеет вид, указанный в табл. 4.4.

Табл. 4.4 – Синтаксисопределенияархитектуры

architecturearchitecture-name ofentity-name is

type declarations

signal declarations

constant declarations

function definitions

procedure definitions

component declarations

Begin

concurrent-statement

. . .

concurrent-statement

endarchitecture-name;

Имя объекта (entity-name) в этом определении должно быть таким же, какое раньше было присвоено объекту в объявлении объекта. Этим самым связывается декларативная и архитектурная части описания объекта.

Имя архитектуры (architecture-name) –это выбираемый пользователем идентификатор, обычно так или иначе связанный с именем объекта; при желании имя архитектуры может быть тем же самым, что и имя объекта.

У архитектуры могут быть также сигналы и другие объявления, являющиеся для нее локальными, подобно тому, как это имеет место в других языках высокого уровня.

В данном пособии нас будет интересовать только объявление сигнала (signaldeclaration). Объявление сигнала сообщает ту же самую информацию о сигнале, какую содержит объявление порта, за исключением того, что вид сигнала (in, out, buffer, inout) не задается:

signalsignal-names : signal-type;

Параллельные операторы

В формате описания архитектуры объекта, секция параллельных операторов {concurrent_statement} содержит один или несколько параллельно выполняющихся операторов, с помощью которых задают зависимость выходных сигналов от входных.

Параллельные операторы это такие, каждый из которых выполняется при любом изменении сигналов, используемых в качестве его исходных данных. Результаты исполнения параллельного оператора доступны для других параллельных операторов не ранее, чем будут выполнены все операторы, инициализированные общим событием. Исполнение параллельных операторовинициируется не по последовательному, а по событийному принципу, т.е. они исполняются тогда, когда реализация других операторов программы создала условия для их исполнения. Таким образом, правило моделирования состоит в том, что в случае, когда последним оператором в теле VHDL-архитектуры изменяется сигнал, используемый в первом параллельном операторе данной архитектуры, программа должна вернуться назад к первому оператору и скорректировать его результаты, приведя их в соответствие с только что изменившимся сигналом. Такой режим исполнения заметно отличается от последовательного выполнения операторов в программном обеспечении, написанном на одном из обычных языков программирования.

Параллельные операторы представляют части алгоритма, которые в реальной системе могут исполняться одновременно. Эти части взаимодействуют между собой и с окружением проектируемой системы.

Последовательность записи параллельных операторов в теле архитектурного описания значения не имеет. Порядок выполнения (или, как говорят обычно, в параллельных вычислениях – порядок срабатывания параллельных операторов) определяется не порядком текстуальной записи операторов между begin и end, а другими правилами. Основным принципом здесь является управление от потока изменений сигналов, входных для параллельного оператора. Изменение значения сигнала, являющегося входным для параллельного оператора, запускает срабатывание данного оператора (т.е. акт выполнения оператора).

Основным параллельным оператором является оператор сигнального присваивания (concurrentsignal-assignmentstatement). Его можно прочесть так: «Сигнал с именем signal-nameпринимает значение выражения expression». Присвоение значения сигналу задают составным оператором “<=”. Логические операторы and, or, nand, nor, xor, хnоr имеют одинаковое старшинство и выполняются слева направо в выражениях. В сложных логических выражениях порядок выполнения операторов регулируется скобками.

В листинге 4.2 представлена архитектура объекта для дешифратора, записанная в потоковой форме.

Листинг 4.2 – Потоковая архитектура для дешифратора

entity DECODER is

port (

A0,A1,E: in BIT;

D0,D1,D2,D3: out BIT

);

end DECODER;

architectureDECODER_archof DECODER is

Begin

D0 <= not A0 andnot A1 and E;

D1 <= A0 and not A1 and E;

D2 <= not A0 and A1 and E;

D3 <= A0 and A1 and E;

endDECODER_arch;

Задание для самостоятельной работы

1. Построить потоковое описание схемы по алгебраическому представлению реализуемых комбинационной схемой функций из темы 3.

2. Осуществить вычисления, задаваемые этим описанием.

Теоретические сведения

Схемы, выходное состояние которых однозначно определяется только комбинацией входных сигналов, называют комбинационными. Законфункционированиякомбинационнойсхемыопределяетсясистемойпереключательных (логических) функций:

|

F1 =f1 ( x1, x2, . . . , xn),

| (5.1) |

Схемы, выходное состояние которых однозначно определяется только комбинацией входных сигналов, называют комбинационными. Закон функционирования комбинационной схемы определяется системой переключательных (логических) функций: F1 = f1 ( x1, x2, . . . , xn ), F2 = f2 ( x1, x2, . . . , xn ), . . . . . . . . . . Fk = fk( x1, x2, . . . , xn ), Синтез комбинационной схемы состоит в построении схемы на основе заданного закона ее функционирования в виде системы переключательных функций или таблиц истинности. При синтезе комбинационной схемы чаще всего необходимо построить схему с использованием минимального числа элементов в заданном элементном базисе, например, на элементах И-НЕ. Задача проектирования комбинационных схем в общем случае не имеет однозначного решения. Наряду с логическими элементами для реализации комбинационных схем применяют схемы со средней и высокой степенью интеграции (ИС-2, ИС-3). Данные схемы сами являются продуктом синтеза, поэтому синтез на их основе комбинационных схем требует иного подхода, чем в случае использования логических элементов. В ряде случаев применение этих схем облегчает задачу синтеза, например, на мультиплексоре или дешифраторе легко реализовать любую функцию от двух, трех или четырех переменных. Существуют специально разработанные микросхемы (программируемые логические матрицы - ПЛМ) для реализации комбинационных схем. Например, на ПЛМ К556РТ1 можно реализовать до восьми логических функций, каждая из которых может иметь до шестнадцати переменных и содержать до сорока восьми конъюнктивных членов. Для реализации комбинационных схем также используют постоянные запоминающие устройства (ПЗУ). На них можно реализовать одновременно столько функций, сколько имеется выходов у схемы ПЗУ, а количество переменных xi определяется количеством адресных входов. ПРОЕКТИРОВАНИЕ ОДНОВЫХОДНОЙ КОМБИНАЦИОННОЙ СХЕМЫ Проектирование одновыходной комбинационной схемы на элементах И-НЕ состоит из следующих шагов: • получение минимальной ДНФ переключательной функции, • представление полученной минимальной формы в базисе Шеффера, • построение по полученному выражению комбинационной схемы. Пусть задана функция F1 от четырех переменных в виде десятичных номеров конституент совершенной дизъюнктивной нормальной формы, т.е. тех наборов, на которых функция равна единице (см. вариант 30 в таблице вариантов): F1 ( x3, x2, x1, x0 ) = (0, 2, 4, 6, 10, 12, 14, 15). Эту функцию необходимо реализовать на элементах И-НЕ. Запишем эту функцию в виде логического выражения: . Минимизация функции Произведем минимизацию заданной функции, используя метод диаграмм Вейча (рис.2.1). Получим следующее минимальное выражение функции: . (2.2) Представление функции в базисе Шеффера Преобразуем полученное выражение (2.2) к виду, удобному для реализации на элементах И-НЕ, т.е. запишем его в базисе Шеффера. Преобразование выполняют по следующим правилам: • все знаки конъюнкции и дизъюнкции заменяют на знаки «штрих Шеффера»; • переменные, входящие в одну импликанту, заключают в скобки; • однобуквенные импликанты инвертируют; • исходное выражение, состоящее только из одной импликанты с числом букв 2 и более, после замены конъюнкции на «штрих Шеффера» инвертируют. Примечание. Обычно легко запоминают первые два пункта правила перехода от ДНФ к функции Шеффера (это наиболее типичный случай) и забывают о частных случаях, отраженных в двух последних пунктах. Проиллюстрируем эти случаи. Пример 1. Пусть полученное минимальное выражение: . Тогда преобразованное выражение будет выглядеть так: Пример 2. Допустим, исходное выражение имеет вид: . После преобразования выражение будет выглядеть следующим образом: В нашем примере получим: (2.3) Построение комбинационной схемы Построение комбинационной схемы выполняют в следующей последовательности: a) вначале с помощью элементов НЕ получают инверсные значения переменных; b) затем, используя элементы И-НЕ, реализуют члены логической функции, заключенные в скобки; c) наконец, выходы элементов И-НЕ, использованных в п. b), подают на входы результирующего элемента И-НЕ. Приведенная последовательность построения комбинационной схемы по полученному выражению (2.3) показана на рис. 2.2. Вначале с помощью инверторов D1 и D2 получают инверсные значения переменных х0 и х3. Затем, используя элементы D3 - D6, реализуют члены логической функции, заключенные в скобки. Наконец, с помощью элемента D7 завершают построение схемы. Рис. 2.2. Реализация комбинационной схемы на элементах И-НЕ Временная диаграмма работы спроектированной комбинационной схемы приведена на рис. 2.3. Рис. 2.3. Временная диаграмма работы комбинационной схемы Из ее рассмотрения можно сделать вывод о соответствии функционирования схемы заданному закону. На вход схемы поступает последовательность сигналов, задающая все 16 наборов, на которых определена функция. Из рис. 2.3 видно, что выход схемы принимает значение 1 на наборах 0, 2, 4, 6, 10, 12, 14 и 15, т.е. спроектированная схема правильно реализует заданную функцию. Динамические параметры комбинационной схемы К динамическим параметрам комбинационной схемы относят задержки переключения выходного сигнала < Наши рекомендации

|