Вычислительная техника. Часть 2.

Вычислительная техника. Часть 2.

ЭВМ и микропроцессоры.

Предыдущая часть курса занятий закончена:

· Счетчиками и разбором курсовой работы по вычислителю

Это, по сути, упрощенная работа микропроцессорной секционированного микропроцессора системы МП К-1804 и ЭВМ.

Для более глубокого изучения этого МП во второй части курса ВТ и ИТ будут рассмотрены разделы:

1) Запоминающие устройства

2) Принципы работы ЭВМ

3) Структура и программирование в МП системе МП К-1804

Запоминающие устройства (ЗУ)

1.1 простейшие ЗУ триггер и регистр рассмотрены в первой части

1.2 ЗУ большой емкости – матричные ЗУ

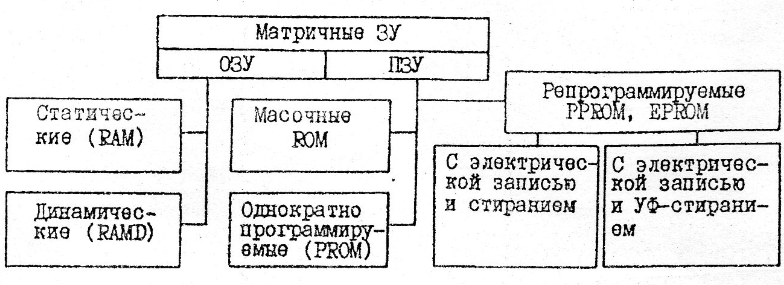

Классификация ЗУ на постоянные ЗУ (ПЗУ) и временного(оперативного) хранения- ОЗУ.

В современных ЭВМ (в том числе персональных) матричные ЗУ используются для хранения больших массивов числовых данных ипрограмм: в обоих случаях записи ихранению подлежат многоразрядные двоичные числа. Пользователь ЗУ должен иметь возможность, указав номер нужной ячейки памяти (адрес), сравнительно быстро записать в нее или считать из нее двоичное число. Часть служебных программ (инициализации, ввода-вывода и т.п.) имеют неизменный текст и должны записываться однократно на постоянное хранение, т.е. требуют для своего хранения постоянных ЗУ (ПЗУ), в которых информация сохраняется даже при отключенном питании (самовосстанавливается при его включении). Большая не часть пользовательских программ и данных, как правило, непрерывно обновляются и требуют для своего хранения оперативных ЗУ (ОЗУ), предусматривающих возможность быстрой многократной записиинформации, которая пропадает, стирается при отключении питания.

Структурная схема классификации ЗУ

На рис. 1.2.1 представлена классификация ЗУ. Следует разобраться в основных типах ЗУ, понять разницу между статическими и динамическими ЗУ. Важным классификационным признаком является .технология изготовления ЗУ: на униполярных ( n-МОH, р- МОH, КMОП, n-ЛИЗМОН) или биполярных (ТТЛ, ТТЛШ. И2Л, ЭСЛ) транзисторах. Основными параметрами ЗУ являются: емкость (число ячеек памяти), разрядность и время обращения.

| Рис. 1.2.1 |

Подробности ОЗУ для ЭВМ.

Устройства памяти или запоминающие устройства ЭВМ выполняется в виде БИС по различным электронным технологиям. Запоминающие устройства (3У) представляют собой комплекс средств для приема, хранения и выдачи данных - чисел., команд, символов, слов из символов и т.п. Комплекс включает в себя средства адресации данных, накопитель данных (запоминающую среду) а устройство управления (местное), синхронизируещее, связывающее весь комплекс.

При любом принципе построения я работы запоминающей среды она состоит из запоминающих элементов (ЗЭ), хранящих один двоичный разряд. По технологии изготовления и тину запоминающих элементов различают биполярные 37 на биполярных транзисторах (ТТЛ- или ЭСЛ- схемы) и МОП-ЗУ с МОП- транзисторами.

Биполярные ЗУ имеет более высокое быстродействие (время выборки 40 - 100 кс и 10-30 но соответственно- для ТТЛ и ЭСЛ-. схем, но меньшую плотность размещения 33 на кристалле и меньшую емкость для одной БИС (256 бит - 4 Кбит), большую стоимость. В биполярном ЗУ запоминающими элементами служат статические триггеры с парафазным управлением (статическая запоминающая среда).

МОП- схемы имеет более простую технологию изготовления, меньшие размеры транзисторов, меньшую потребляемую мощность, благодаря этому МОП-ЗУ имеет значительно большую емкость для одного кристалла (корпуса) (4 -- 64 Кбит), значительно меньшую удельную стоимость, но существенно большее время выборки (2СО-350 но). В МОП-ЗУ запоминающим элементом макет быть либо триггер, тогда это статическое МОП-ЗУ, либо МОП- транзистор, на емкости затвор- исток которого в течение некоторого времени сохраняется электрический заряд - носитель информации. Этот заряд периодически необходимо поддерживать, регенерировать запись данных, поэтому такие МОП-ЗУ называется динамическими.

Запоминающие элементы в кристалле образуют плоскую матрицу с двумя координатам X и Y , матрица хранит один, одноименный, разряд всех слов. Для организация ЗУ п -разрядных слов используют параллельно n кристаллов, БИС. Каждый кристалл имеет адресное и разрядное управление. Разрядное управление содержит усилитель записи и усилитель считывания для нулевой разрядной фазы линии запоминающих элементов и точно такие же усилители для единичной разрядной фазы. Адресное управление содержит два дешифратора: .для координаты X и координаты Y .

ГГо заданному коду адреса обращения дешифраторы выбирают по одной своей выходной шине xi и yi; эти шины управляют горизонтальными и вертикальными линиями запоминающей матрицы; в результате при всяком обращении оказывается выбранным единственный ЗЭ -элемент, находящийся на пересечении выбранных шин хi и yi . При обращении для считывания выбранный ЗЭ выдает на разрядные линии сигнал, соответствующий его состоянию, при обращении для записи сигнал с разрядных линий воздействует на состояние выбранного S3, устанавливая его в "I" и "0", и не затрагивает состояния остальных ЗЭ матрицы.

Запоминающие устройства классифицируются по различным признаками на оперативные (ОЗУ), постоянные (ПЗУ), перепрограммируемые или полупостоянные (ППЗУ) и внешние (БЗУ). Оперативными называются запоминающие устройства, имеющие прямую, непосредственную, т.е. оперативную связь с процессором. Интервалы времени обращения к оперативной памяти входят в машинный цикл ЭВМ, команды процессора адресуются к оперативной памяти. Как правило, хотя и не обязательно, ОЗУ работают как на считывание, так и на запись данных, иначе говоря, хранят сменяемую информацию. Характеристики ОЗУ: быстродействие и емкость - прямо влияют на характеристики ЭВМ или системы в целом, т.е., например, для быстродействующих ЭВМ требуются быстродействующие и имеющие большую емкость запоминающие устройства для использования в качестве оперативных.

Матричное ОЗУ

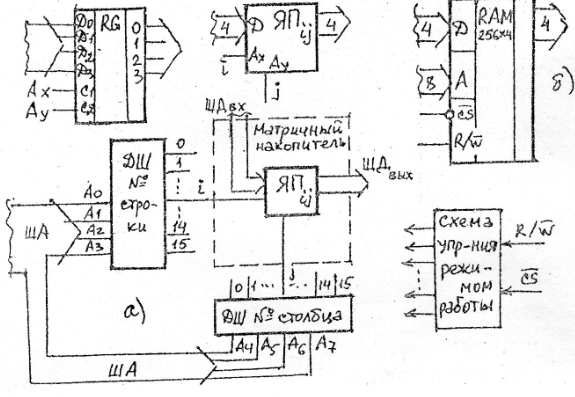

В ОЗУ в узлах матричного накопителя в качестве ячеек памяти используются регистры (триггеры). По этой причине по сравнению с ПЗУ резко возрастают габариты и уменьшается емкость. Главная задача при построении матричного ОЗУ заключается во вводе/выводе информации в любую ячейку по одной шине данных (ШД). Эта задача в принципе просто решается с помощью мультиплексирования, т.е. подключения входов всех регистров к входной ШД, всех выходов – к выходной ШД: при этом проблема адресации к нужной ячейке памяти (ЯП) решается посредством анализа содержимого шины адреса (ША) с помощью двух ДШ номера строки и номера столбца, которые «реанимируют» только одну ЯПij, формируя высокие потенциалы только на i-м и j-м выходах и подавая их на адресные входы Ах и Ау нужной ЯП. (рис. 1. 2.3)

| Рис. 1.2.3 |

| Ячейки памяти (регистры) |

В ОЗУ такого типа возможен произвольный порядок (доступ) обращения к ЯП; в ОЗУ же с последовательным доступом – только в порядке возрастания/убывания адресов (как, например, в стенке или ЗУ на магнитных лентах). Следует обратить внимание на программную реализацию стека в специально выделенной области ОЗУ, когда адреса формируются отдельным реверсивным счетчиком, называемым указателем стека.

1.2.2.1; 1.2.3.1; 1.2.4.1.

Подробности об ОЗУ и ПЗУ.

Характеристики современных БИС ЗУ, используемых для построения ОЗУ, приведены в табл. I [2].

Таблица I

| Марка БИС ЗУ | Тип ЗУ | Емкость | Время Чтения или записи, не | Технология | Потребляемая мощность, МВт/бит | Напряжение питания, В | |

| К541РУ1 | статическое | 4096x1 | И2Л | 0,11 | +5 | ||

| КР537РУ2 | статическое | 4096x1 | кМДЦ | 0,07 | +5 | ||

| К566РУ1 | динамическое | 4096x1 | ЦДЛ | 0,175 | +5, н12 | ||

| К565РУЗ | динамическое | 16384x1 | Мдп | 0,03 | +5,+12 | ||

Перейдем к рассмотрению ПЗУ. Постоянными называются ЗУ, которые по своим конструктивным особенностям могут хранить только постоянную, не изменяемую информацию. В таких ЗУ хранимая ими информация заносится в устройства однажды и не изменяется в процессе работы ЭВМ или системы; ПЗУ работают в системе только на считывание данных, но не на запись. ПЗУ имеют другие названия: односторонние, долговременные, пассивные ЗУ. Смысл применения постоянных ЗУ в том, что, с одной стороны, при обработке данных часто встречаются наборы данных, не изменяющиеся в процессе всей "жизни" системы; с другой стороны - конструкция постоянного ЗУ, имеющего упрощенную функцию, имеет определенные достоинства перед оперативным ЗУ, работающим и на запись, и на считывание. К неизменяемым наборам данных относятся микропрограммы устройства управления (см. с. 27 ), тест-программы контроля исправности устройств, табличные функции, библиотеки стандартных программ, программы инициализации операционной системы и др.

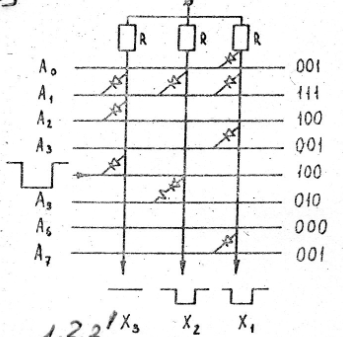

Если в ЗУ следует хранить постоянную информацию, ее можно записать и хранить не электрическим, а механическим способом, это позволит получить лучшие характеристики. Далеким прототипом ПЗУ можно считать старинные музыкальные шкатулки, в которые запись заносилась раз и навсегда соответствующим расположением механических пуансонов на образующей поверхности вращающегося барабана. Принцип построения современных ПЗУ можно понять из рис. 1.2.3.1

Рис. 1.2.3.1 Принцип работы ПЗУ

,

ПЗУ образовано прямоугольной матрицей, имеющей адресные шины Aiи разрядные шины xi . Одна ячейка ЗУ, хранящая слово, образуется одной горизонтальной шиной адреса, Ai «I»в j– й разряд i -го слова реализуется включением диода в пересечение j -ой разрядной и i -ой адресной шин; пересечение адресной и разрядной шин, не содержащее диода, хранит "О". Дешифратор адреса ПЗУ преобразует код адрес обращения к ПЗУ в возбуждение одной соответствующей адресной шины Ai . Возбуждение шины выражается в том, что на ней появляется единичный сигнал, на остальных шинах при этом сохраняется нулевой сигнал. В рассматриваемой примере нулевой сигнал является закрывающим для диодов, а единичный – открывающим. Таким образом, в результате выбора одной адресной шиш на разрядных шинах появится набор сигналов, соответствующих записи на выбранной шине.

Технологически проще записывать информацию в ПЗУ на основе следующего общего метода. Вначале изготовляется матрица, содержащая диоды во всех пересечениях, затем "удаляются" диоды из тex пересечений. где должен храниться "О". "Удаление" диода из ячейки производится разрывом одного из проводников, связывающих диод с шинами. Для этой цели последовательно с каждым диодом имеется перемычка из нихрома, она при определенной величине тока сгорает, расплавляется, разрывая цепь (перемычка показана условно в пересечении А5 X2 ), Запись информации в матрицу производится на специальных стендах, программаторах, которые создают необходимый электрический режим, последовательно выбирают пересечения в матрице я подают большой, перелагающий ток в пересечения, куда следует записать "О".

В качестве элементов, включаемых в пересечения шин матрицы, кроме диодов могут использоваться транзисторы или эмиттеры многоэмиттерных транзисторов. ПЗУ обеспечивают большую плотность упаковки информации в кристалле, чем ОЗУ, важнейшим достоинством ПЗУ перед ОЗУ служит то, что оно энергонезависимо, т.е. отключение электрического питания не приводит к утрате хранимой информации.

Очень важной разновидностью ПЗУ являются программируемые логические матрицы (ПЛМ) [4] . ПЗУ можно считать комбинационной цифровой схемой, реализующей некоторую функцию булевой алгебры. Возможности ПЗУ в этом смысле универсальны - оно может реализовать любую булеву функцию, для этого достаточно занести в матрицу соответствующие записи. Ограничения накладываются лишь объемом памяти, т.е. числом переменных булевой функции. Ограничения мокко- существенно ослабить, если строить матрицу специализированно, более экономично. Такое построение ПЗУ получило название ЦВМ. ГШ строится в виде последовательного соединения матрицы декодера (дешифратора) и матрицы кодера (шифратора), такая композиция универсальна - может реализовать любую булеву функцию.

ПЛМ, как и ПЗУ общего вида, могут программироваться, т.е. приобретать конкретную запись при изготовлении на заводе-изготовителе, в этом случае они содержат некоторые стандартные функции и могут программироваться пользователями и выполнять в этом случае любые, не стандартные функции.

2.1.2

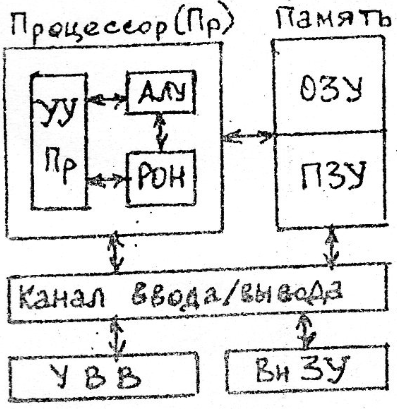

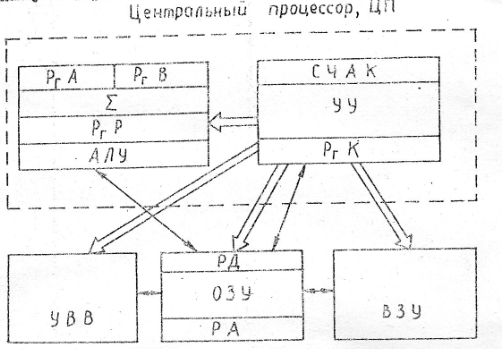

Принцип программного управления предписывает и исходные данные, и команды программы в виде многоразрядных двоичных чисел (машинных слов, кодов) размещать з памяти ЭВМ: при этом каждое слово идентифицируется номером (адресом) соответствующей ячейки памяти. На рис. 2.2.1 изображена обобщенная структурная схема ЭВМ: основные устройства (модули) ЭВМ - это процессор (Пр) и память. Процессор обеспечивает поочередную выборку команд программы из памяти и их выполнение, т.е. реализует программное управление. Основная память и Пр составляют ядро ЭВМ.

В своем составе Пр имеет АЛУ, собственное ОЗУ небольшой емкости в виде блока регистров общего назначения (РОН) и устройство управления (УУ), организующее совместную работу всех узлов Пр. Устройства ввода/вывода Рис. 27 '(УВВ) служат для связи с внешним

| Рис. 2.2.1 |

В процессе Функционирования процессор циклически повторяет следующие действия (командный цикл):

1) выборка кода очередной команды программы из ОЗУ;

2) анализ кода, определение типа операции и количества операндов;

3) определение местонахождения (адреса) операндов и их выборка из ОЗУ;

4) выполнение над ними заданной операции;

5} вычисление .адреса для выборки следующей команды.

Адрес первой команды (стартовый адрес программы) вводится оператором или формируется автоматически при включении питания.

2.1.3

В настоящее время определились два главных направления в развитии средств ВТ; создание персональных микроЭВМ (ПЭВМ) и высокопроизводительных суперЭВМ. Последние строятся на основе многопроцессорных систем с использованием транспьютерных СБИС и с применением спецметодов (распараллеливание вычислений) организации вычислительного процесса.

2.2 Подробности и алгоритм выполнения программы.

Укрупненная структурно-функциональная схема ЭВМ представлена на рис.2.2.1, здесь изображено разделение ЭВМ на наиболее крупные компоненты по функциональному признаку, компонента называются соответствующими устройствами и показаны взаимосвязи устройств, Рассмотрим кратко функции устройств.

Оперативное запоминающее устройство (ОЗУ), иначе - основная память - предназначено для хранения программ и данных, чаще всего работает по адресному, точнее - прямоадресному принципу. Это значит, что ОЗУ выдает и принимает данные по указанию их прямого адреса, т.е. номера места в ОЗУ, ячейки. Цикл работы ОЗУ называется обращением, за обращение производятся запись или считывание одного слова данных. Записываемое слово подается на регистр данных (РгД), адрес подается на регистр адреса (РгА) и после этого выполняется цикл ОЗУ для записи; прежнее содержимое ячейки, в которую производится запись, утрачивается. При обращении для считывания на РгА подается адрес и запускается цикл считывания, считанное слово принимается из ОЗУ на РгД, причем в ячейке оно сохраняется. Функционально ОЗУ разделяется на запоминающую и управлявшую части.

| Рис. 2.2.1 |

Основными техническими характеристиками ОЗУ служат длительность обращения я емкость, т.е. число слов, которое можно хранить в нем одновременно.

Внешние запоминающие устройства (ВЗУ) применяются с целью наращивания общей емкости памяти ЭВМ, поскольку емкость ОЗУ недостаточна. ВЗУ строятся на магнитных дисках, лентах, гибких магнитных дисках и др.

Устройства ввода и вывода данных предназначены для обеспечения взаимосвязи ЭВМ с окружающей средой - человеком, множеством людей, оконечными устройствами линий связи, информационно-измерительными системами и др.

Арифметико-логическое устройство (АЛУ) преобразует данные, форму информации, подаваемой в, него из ОЗУ, и возвращает данные в ОЗУ. Иначе говоря, АЛУ выполняет операции над данными числами, символами, адресами, например, операции сложения, умножения, сравнения и др. Чтобы выполнить операцию в АДУ необходимо подать в него операнды, указать операцию и запустить его. А1У разделяется на две части по функциональному признаку: операционный автомат (OA) и управляющий автомат (УА). Технической характеристикой АЛУ служат времена исполнения им операций.

Устройство управления (УУ) управляет остальными устройства, ми ЭВМ, оно передает в управляемое устройство исходные данные, запускает управляющую часть устройства и воспринимает от нее сигнал окончания работы устройства. Таким образом, УУ организует работу а взаимодействие всех устройств в ЭВМ, регламентирует ее во времени. Периодом работы УУ служит исполнение ЭВМ одной команды, так называемый машинный цикл. Технической характеристикой УУ и одновременно ЭВМ в целом служит быстродействие - среднее число машинных циклов, исполняемых ЭВМ в I с.

Два устройства, АЛУ и УУ, вследствие того, что они тесно взаимосвязаны, т.е. взаимодействуют в течение машинного цикла, часто рассматриваются совместно, как тандем. Этот тандем имеет специальное название "процессор".

ЭВМ автоматически исполняет программы или микропрограммы, написанные на алгоритмических языках или машинных языках программирования. Иначе говоря, ЭВМ реализует алгоритм выполнения программ, написанных на определенных языках.

Пусть программа на машинном языке и исходные данные находятся в ОЗУ ЭВМ.

Алгоритм выполнения программ, написанных на машинном языке, может быть сформулирован следующим образом (представлен следующими шагами):

1. Выбрать из ОЗУ очередную команду программы.

2. Выбрать операнды,' указанные (определенные) командой.

3. Выполнить над операндами операцию, указанную командой.

4. Полученный в шаге "3" результат направить в указанное (определенное) командой место.

5. По указанию, имеющемуся в команде, и по признакам полученного в "3" результата определить место в ОЗУ команды, подлежащей исполнению следующей, т.е. место очередной команда.

6. Перейти к "I".

Таким образом, процесс реализаций программы есть последовательность стандартных (или стереотипных) циклов из шагов (1-6), называемых машинными циклами.

Алгоритм (1-6) представлен, разумеется, в укрупненной общей форме, здесь не показаны явно многочисленные частные ветви, реализуемые алгоритмом выполнения, а также не рассматриваются методы определения первой команды программы и остановки процесса.

Обратимся теперь к рис 2.2.1 и интерпретируем шаги алгоритма выполнения (1-6) в терминах структурной схемы ЭВМ.

Шаг I. Устройство управления УУ считывает из ОЗУ код очередной команды программы и помещает его б свойрегистр команд (РгК). В течение последующих шагов цикла код команды в РгК определяет управление, т.е. управляющие воздействия, микрокоманда, формируемые и направляемое на другие устройства устройством управления (УУ).

Шаг 2. УУ читает на РгК код операции и бзависимости от наго по тему или иному алгоритму формирует адреса операндов. Формирование происходит из кодов определенных полей команды к . кодов, хранимых в УУ, с помощью средств (узлов)УУ или средств АЛУ. При этом УУ совместно о АЛУ выполняет некоторую последовательность микрокоманд. Сформировав адрес операнда, УУ передает его ОЗУ (на РгА) и запускает последнее с целью выборки. Посте срабатывания ОЗУ, т.о. считывания операнда, УУ передает его из ОЗУ (РгД) в АЛУ. Эта процедура повторяется столько раз, сколько операндов требуется извлечь из ОЗУ для выполнения команды в зависимости от макета команды и исполняемой операции.

Шаг 3. УУ передает из РгК код операции (КОП) в АЛУ и запускает его. Все необходимое для наполнения операции (операнды, операция) имеется в АЛУ, оно выполняет операцию или автономно, под управлением своего управляющего автомата, или под управлением УУ, реализуя определенную последовательность микрокоманд- микропрограмму. Окончив исполнение операция, сформировав результат и признаки результата, АЛУ сообщает об окончании операции в УУ.

АЛУ характеризуется средним числом операций в секунду, которое оно исполняет при полной загрузке, т.е. быстродействием АЛУ, а также - длиной разрядной сетки, формами представления данных, составом операций, встроенных в АЛУ (так называемая сигнатура

операций).

Шаг 4. На основе кода операции(K0II)УУ распоряжается результатом: результат либо, остается в АЛУ, при этом УУ перемещает его в определенный регистр АЛУ, либо он засылается в ОЗУ. В последнем случае УУ по КОП к определенному полю в РгК формирует адрес засылки результата, передает его на РгА, передает результат из АЛУ в РгД и запускает в ОЗУ обращение для записи. Эти процедуры, как и выше, исполняются в виде последовательности микрокоманд.

Ш а г 5. Для определения следующей команда (ее места в ОЗУ) пользуются одним из двух методов: первый метод навивается методом естественной адресация команд, он полагает, что следующая команда хранится в ОЗУ следом за текущей. Это значит, что, зная адрес начала кода текущей команда и длину текущей команда, можно вычислить адрес начала следующей команды. Нередко команды имеют фиксированную длину и, во всяком случав, фиксированный набор длин, поэтому вычисление адреса удобно выполнять на основе счетчика, который в начале машинного цикла показывал бы адрес начала текущей команды, а затем прибавлял бы к своему содержимому длину кода текущей команда. Такой счетчик называется счетчиком адреса команда (СЧАК).

Переходы в программе - условные и безусловные, - нарушающие естественный порядок следования исполняемых команд в соответствии с их расположением в тексте программы, реализуются в форме исполнения команд перехода. То есть в случае перехода следующая команде определяется посредством выполнения специальной команда, машинного цикла, а не одного пятого шага.

Если для алгоритмов (программ) характерно большое число переходов, естественный метод адресации команд становится нерациональным, так как требует большого числа дополнительных машинных циклов. В этом случае применяется второй метод – метод принудительной адресации команд. Каждая команда содержит в своем коде поле, указывающее адрес следующей команды. Этот адрес, в зависимости от КОП, задается либо безусловно, либо условно. В последнем случае по признаку результата, полученному в третьем шаге текущего цикла, УУ выбирает в пятом шаге либо адрес из кода команды, либо – следующий за адресом текущей команды. Ясно, что второй метод адресации команд не нуждается в отдельных командах перехода, однако и он имеет недостаток – дополнительные затраты пространства памяти на хранение полей адресов.

После определения адреса команды он передается из УУ на РгА ОЗУ. На этом пятый шаг цикла заканчивается. Разумеется, пятый шаг, так же как и предыдущие шаги, при реализации складывается из последовательности более мелких шагов - из последовательности макрокоманд.

Шаг 6. Выполняется возврат в начало машинного цикла – шагу 1. Адрес следующей команды, необходимый для выполнения первого шага, подготовлен и находится на РгА ОЗУ.

Разумеется, изложенный алгоритм выполнения программ в ЭВМ – некоторый типовой и упрощенный, освобожденный от многочисленных деталей и вариантов, однако именно изложенный вариант составляет "костяк", магистраль различных конкретных реализаций данного алгоритма. Алгоритм выполнения необходимо хорошо изучить, свободно владеть им с тем, чтобы узнавать его типовые элементы в дальнейших конкретных, более сложных примерах.

Подведем первый итог изученного. Мы познакомились с типовой структурно-функциональной схемой ЭВМ и далее с алгоритмом выполнения программы, реализуемым этой схемой. ЭВМ посредством взаимодействия своих устройств читает созданную человеком программу как инструкцию и пополняет прочитанное, т.е. работает под управлением программы. Чтение и исполнение производится покомандно, интервал исполнения команды составляет стандартный машинный цикл. Цикл разделен на относительно крупные шаги, последние – на мелкие, микрокоманды.

Изученное позволяет также определить важное понятие архитектуры ЭВМ. Под архитектурой ЭВМ будем понимать структурную схему ЭВМ и совокупность характеристик, параметров ЭВМ, существенных для использования ЭВМ, определяющих качество, возможности ЭВМ. Иначе говоря, архитектура - совокупность характеристик, которыми руководствуется пользователь при выборе ЭВМ или постановке задачи на заданной ЭВМ. Ясно, что в названную совокупность входит большой перечень параметров, мы назовем только некоторые, наиболее важные и понятные после изученных разделов. Отметим, что в процессе применения ЭВМ пользователи имеют дело с комплексом из аппаратурной основы (собственно ЭВМ) и программной надстройки (операционная система, базы данных и др.), поэтому следует различать архитектуру того и другого. В нашем курсе рассматривается исключительно аппаратурная часть ЭВМ и соответственно только ее архитектура.

Итак, архитектуру ЭВМ определяют ее структура, быстродействие, емкость ОЗУ, емкость ВЗУ и их типы, длина разрядной сетки чисел и команд, сигнатура операций и команд, формы представления чисел (наличие формы с плавающей запятой) и др.

Типы микропроцессоров.

Секционированный МП КI804

Секционированный или разрядно- модульный МП - другой вариант архитектуры МП. В отличие от однокристального МП в данном случае структурная схема процессора "разрезана" на секции и каждая секция выполнена на отдельном кристалле, БИС; все БИС секций в совокупности образуют МПК, Как правило, АЛУ с абонированного МП "разрезается" вертикалями, т.е. членится па одинаковые к- разрядные модули, секция; такая секция, содержащая кроме АЛУ другие фрагменты процессора, называется центральным процессорным элементом (ЦПЭ), а упрощенно - МП (микропроцессор)или ЦП(центральный процессор). Для получения необходимой разрядности микропроцессора используется соответствуйте число ПЦЭ, объединенных для параллельной работы под единых управлением.

Второе важнейшее отличие секционированного МП состоит в том, что его устройство управления строится по принципу микропрограммного управления. Это значит, что при создании МПК зафиксирован только набор МККД, МПКМ из них создает сам пользователь; поэтому МПК содержит БИС памяти MKDM и БИС устройства МКГМ управления.__

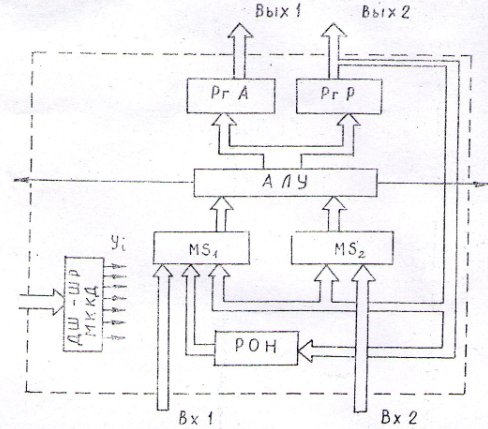

Типовая структура ЦПЭ секционированного МП представлена на рис. 2.5.1. Здесь имеются АЛУ, локальная память на РОН емкостью 8 - 16, два мультиплексора на входах АДУ, • коммутирующее различные источники на регистры-приемники АЛУ, выходные регистр адреса (РгА) и регистр результата АЛУ (РгР), входные н выходные магистрали, дешифратор-шифратор микрокоманд ЦПЭ. Последний получает из УУ позиционный код МККД и преобразует его в пространственную последовательность "I" и "О" - управляющие сигналы, поступающие на шины узлов ПЦЭ, Исходные данные (операнды) поступает по магистрали Bх.I из ОЗУ или по магистрат Вх. 2 из устройств ввода, данных через мультиплексор в АЛУ. Результаты из АЛУ принимаются в РгР  Рис. 2.5.1 Типовая структура ЦПЭ секционированного МП: MS1, MS2 - мультиплексоры; ДШ-ШP МККД - дешифратор-шифратор микрокоманд МП

Рис. 2.5.1 Типовая структура ЦПЭ секционированного МП: MS1, MS2 - мультиплексоры; ДШ-ШP МККД - дешифратор-шифратор микрокоманд МП

или РгА, а также в РОН. Результаты отправляются в ОЗУ или устройства вывода по магистрата Вых.2 по адресу, передаваемому по магистрата Вых. I. Связь с другими секциями ЦПЭ осуществляется по линиям межразрядных связей АЛУ, передавших и принимающих перенос и значения сдвигаемых разрядов при операциях сдвига; АЛУ выдает также вовне значения признаков результата (в описаниях МПК они обычно называются «флагами» АЛУ).

Видно, что структура ЦПЭ аналогична структуре однокристального МП, разница между ними в том, что сложное УУ однокристального МП в секции ЦПЭ отсутствует; в последнем имеется только средство реализации готовой МККД - дешифратор- шифратор; МККД в ЦПЭ подает секция микропрограммного управления, считывая ее из памяти микропрограмм.

Задача, решаемая УУ с микропрограммируемой логикой, относительно проста - в каждом цикле поставлять в управляемые секции и устройства (ЦПЭ, ОЗУ, УВВ) код микрокоманды, его интерпретация в виде пространственной последовательности "I" и "О" выполняется в управляемых секциях. МКПМ хранятся в памяти, ее (в зависимости от организации ЭВМ) функционально следует отнести либо к УУ, либо к ОЗУ, мы будем называть ее памятью МКПМ. Считанная из памяти МКПМ очередная МККД принимается на Рг МККД и в течение цикла управляет работой секций.

Второй компонент УУ – БМУ(блок местного управления), основное назначение БМУ - определять адрес очередной МККД в памяти МКПМ. Код МККД представляет собой слово (длиной несколько десятков двоичных разрядов), разделенное на несколько полей, отличающихся функциональным назначением и принадлежностью к различным управляемым устройствам: имеется поле ЦПЭ, поле БМУ, поле ОЗУ и УВВ. Поле ЦПЭ содержит код, определяющий все необходимое для выполнения цикла в ПЦЭ - операцию в АЛУ, источники операндов, приемник результата, непосредственное данное (операнд, перенос),

БМУ, управляющий определением адреса следующей МККД в памяти МКПМ, сам управляется соответствующим полем текущей МККД, полем ЕМУ, обозначит его Р. Поле Р указывает тип перехода к следующей МККД - последовательный переход, безусловный переход, условный переход. В первом случае БМУ прибавляет константу к адресу текучей МККД, в частном случае- единицу: РгА= РгА + I.

Перехода в МКПМ реализуются на основе метода принудительной адресации т.е. МККД содержат поле адреса следующей МККД, обозначим его В R, на последовательных участках МКПМ это поле не используется. В случае безусловного перехода БМУ, по указанию поля Р, определяет в качестве адреса следующей МККД адрес из поля В R в текущей МККД, РгА : = BR. Имеются разновидности безусловного перехода, одна из них - переход с возвратом, применяемый для обращения к подмикропрограммам (подМКПМ). При совершении такого перехода БМУ должен запомнить адрес текущей МККД; в конце подМКМП стоит МККД возврата, исполняя ее, БМУ прибавляет константу к сохраняемому адресу и результат выдает в качестве адреса следующей МККД.

Другая разновидность безусловного перехода - определение в качестве адреса следующей МККД поля КОП регистра команд (РгК) ЭВМ. Подобный переход необходим по окончании текущей МКПМ для выхода на начало другой МКПМ, соответствующей очередной команде программ. Для совершения данного перехода последняя МККД текущей МКПМ указывает БМУ передать КОП из РгК в адресный регистр памяти МКПМ: РгА := РгК (КОП). В ячейках с номерами КОП i хранятся МККД безусловного переходам по фиксированным адресам, с которых начинаются МКПМ i- х команд.

При условном переходе поле Р, указывая тип перехода, указывает и признак- условие перехода, например отрицательней знак результата, полученного в АЛУ в предыдущей МККД. Если признак имеет истинное значение, переход совершается, т.е. БМК передает на РгА код из поля ВR , в противном случав переход не делается. БМУ модифицирует на константу адрес текущей МККД и результат выдает в РгА.

Описанные функции БМУ технически могут быть реализованы по-разному. В МПК К589 БМУ реализован в виде логической схемы, в IDE KI804 - в виде логической схемы определения адреса и ПЗУ, хранящего логику переходов и выдающего управляющие сигналы на логическую схему. В МЦК KI804 два разряда, поля Р - разряды P1 P0 -подается с регистра МККД на мультиплексор наделения признаков ПЦЭ, выход мультиплексора, назовем его ϕ , присоединяется к коду P3 P2 P1 P0 поля P полученный 5-разрядный код ϕ подается на ПЗУ в качестве адреса A4 A3 A2 A1 A0; выходное слово ПЗУ восьмиразрядное Q7/Q0 подается на шины логической схемы

определения адреса ШУ. Под действием сигналов Q7/Q0 слова, выбранного из ПЗУ, логическая схема либо переписывает поле ВR из регистра МККД в РгА памяти МКПМ, либо прибавляем единицу к текущему значению РгА.

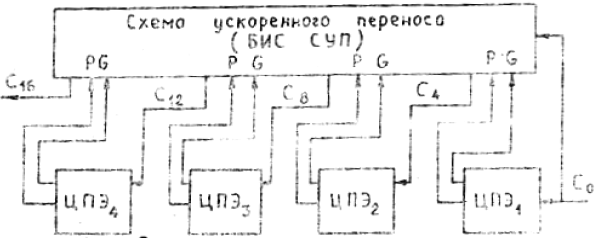

Кроме рассмотренных БИС (секций) ЦПЭ, БМУ и памяти МКПМ, в МПК обычно имеется БИС схема ускоренного переноса (СУП) (рис. 2.5.2) обеспечивающая быструю передачу переноса между секциями ЦПЭ, ИС многорежимного буферного регистра (МБР), ИС блока приоритетного прерывания (БПП), ИС шинного формирователя (ЕВ). Используемые при сборке микро- ЭВМ микропроцессорных систем.

Рис. 2.5.2 Организация условного переноса

Ниже оценивается система ШКД секционированного МП KI804, этот комплект выполнен по технологам ТТЛШ, предназначен для светец высокого быстродействия (тактовая частота до 8 МГц) и имеет типичную для секционированного МП систему МВД. Секция цпэ имеет разрядность 4, локальная память содержит 16 РОН.

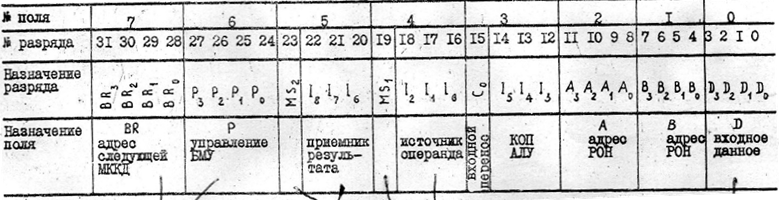

Макет представлен на рис. 2.5.3.

Микрокоманды операций(МККО) или микрокоманды действий(МККД)

Это расширенная структура микрокоманд, рассмотренных в курсовой работе.

:

| Адрес следующей МКК |

| Тип перехода на один разряд(P3…P0) |

| Наличие поля «выходные данные» (Д3..Д0) |

| Наличие полей для приемника результата (Y8..Y3) c МС2 |

| Наличие полей источника операнды (Y2..Y0) c МС1 |

В вышеизложенных выносках рассмотрены отличия от ранее рассмотренной(в курсовой работе) структуры микрокоманд.

Микропрограмма имеет длину 32 разряда и разделена на восемь полей, поле №0 предназначено для непосредственного указания данного, вступающего в операцию. Поле №1 адресует операнд B указанием номера РОИ, в которой находима операнд, т.е.. поле I прямо адресует операнд В из РОН. Поле №2 прямо адресует операнд А из РОН. Поле №3 содержи кед операции КОП, подлежащей выполнению АЛУ(Со). Поле №4 указывает источники операндов. В 19-м и 23-м разрядах расположены модификаторы операций сдвига MS1 и MS2. Поле кодирует приемник результата операции, т.е. указывает куда отправляется результат. Поле №6- поле управления БМУ, т.е. определяющее алгоритм выбора следующей МККД.

На рис. 2.5.4 показана расшифровка кода операции АЛУ, КОП, АЛУ; на рис.2.5.5- расшифровка кода источников операндов АЛУ; на рис. 2.5.6 расшифровка кода приемн