Структуры микропроцессорных ИУВС.

Для современного этапа развития ИУВС характерен переход от ИУВС с

одним микропроцессором к мультимикропроцессорным ИУВС (mМП

ИУВС), в которых сложнейшие задачи управления выполняются

одновременно множеством микропроцессоров. Интерес к созданию

управляющих и вычислительных систем, получаемых соединением в

сложную структуру большого числа микропроцессоров, запоминающих

устройств, устройств ввода-вывода информации, то есть к mМП ИУВС,

обусловлен:

1) необходимостью создания высокопроизводительных ИУВС с

эквивалентным быстродействием в десятки и сотни миллионов операций в

секунду, например для анализа и прогнозирования погоды, распознавания

образов, систем автоматизированного проектирования, решения задач

обработки сигналов и сопровождения целей в военной технике и тому

подобное;

2) требованием обеспечения живучести ИУВС, работающих в режиме

реального времени, то есть необходимостью создания ИУВС, способных

продолжить работу при выходе из строя отдельных их устройств;

3) территориальной удаленностью на десятки, сотни и тысячи метров

элементов систем управления и сбора информации, включающих

вычислительные средства;

4) необходимостью в большинстве случаев коммутации вычислительной

мощности, ее динамическим перераспределением в зависимости от динамики

решаемых задач;

5) необходимостью адаптации ИУВС к внешним условиям, а не наоборот;

6) требованием достижения гибкости вычислительных средств, то есть

возможности изменения конфигурации, расширяемости и модульности

структуры;

7) потребностью в повышении производительности самих микро-

процессоров, поскольку они не могут конкурировать со сверхбыст-

родействующими ЭВМ;

8) низкой стоимостью элементной базы (БИС микропроцессорных

наборов, ОЗУ, ПЗУ, ППЗУ, УВВ), обладающей достаточно большими

вычислительными возможностями.

Успех широкого применения mМП ИУВС связан:

- с разработкой архитектуры (структурной организации) и системного

программного обеспечения;

- с созданием параллельных алгоритмов решения задачи и

соответствующего прикладного программного обеспечения.

Архитектуру параллельных мультимикропроцессорных вычислительных

систем вообще можно классифицировать, например, по типу

внутрисистемных связей, связанности микропроцессоров, по тому, состоит

ли система из однородных или неоднородных вычислительных средств, и

тому подобное. Глобально mМП системы можно разбить на две группы:

а)пирамидальные и б)распределенные.

Рисунок 3.3 - Примеры связей между модулями

мультимикропроцессорной ИУВС распределенного типа

Наиболее экономичным является применение специального класса (δ-

класс) коммутационных сетей («всех со всеми»). В этом случае общая

магистраль как таковая исчезает, так как она растворяется во всевозможных

парных связях между объектами модулей, образующих так называемую

дельта-сеть С (рисунок 3.3в).

Изложенный материал для восприятия является непростым и требует

глубоких знаний в области микропроцессорной техники. Но таковы по

сложности современные системы контроля и управления, ориентированные

на максимальное использование микропроцессорной техники в виду

эффективности последней. По мере продвижения по разделам данной книги

еще не один раз придется обращаться к материалам данного раздела.

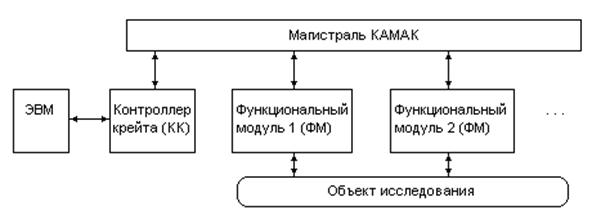

Система КАМАК.

КАМАК представляет собой систему, предназначенную для связи измерительных устройств с цифровой аппаратурой обработки данных. Система построена по модульному (блочному) принципу. Наименьшая конструктивная единица системы - функциональный модуль (или станция) представляет собой вставную кассету. Кассеты размещаются в каркасе-крейте.

Структура измерительной системы на основе аппаратуры КАМАК

Логический стандарт

Модули крейта КАМАК управляются определенным набором команд. Команды делятся на:

- адресуемые (предназначенные конкретному модулю) и

- неадресуемые (общие).

Все адресуемые команды имеют форму NAF, где N - "адрес" - номер станции, на которой расположен модуль (может принимать значения от 1 до 23), A - "субадрес" - номер адреса устройства (регистра) внутри модуля, принимает значения от 0 до 15, F - код операции (функции), которую должен выполнить модуль. Для кодирования операции отводится 5 двоичных разрядов, т. е., это может число от 0 до 31. Каждый модуль может выполнять ограниченное число операций, и, приступая к работе с конкретным модулем, надо по его описанию ознакомиться со списком его функций и соответствующими кодами. Однако существуют общепринятые коды для типичных операций.

| Код команды (F) | Подгруппа операций | Комментарии |

| 0 - 7 | Чтение | F (2) - чтение и сброс содержимого регистра |

| 8 - 15 | Управление | F (8) - поверка L-запроса; F (9) - сброс L-запроса |

| 16 - 23 | Запись | - |

| 24 - 31 | Управление | F (24) - блокирование; F (25) - исполнение; F (26) - деблокирование; F (27) - проверка состояния |

Безадресные команды, действующие на все станции крейта:

- "подготовка" (Z) - устанавливает все матрицы в исходное состояние;

- "запрет" (I) - на время действия сигнала выполнение команд прекращается;

- "сброс" (C) - устанавливает в исходное состояние отдельные регистры модулей.

Адресуемые и неадресуемые команды генерируются контроллером и воспринимаются модулями. Кроме этого, есть ряд сигналов, генерируемых модулями. К ним относятся:

- запрос на обслуживание (L-запрос);

- ответ блока (Q-сигнал) (как правило, возникает по выполнению определенной команды);

- сигнал занятости линии (В-сигнал);

- сигнал "команда принята" (X-сигнал) (указывает на то, что команда принята и правильно декодирована модулем).

Текущее состояние аппаратуры КАМАК отображается соответствующими индикаторами на передней панели крейта. Программное управление и определение состояния аппаратуры осуществляется через регистр управления и состояния - РУС (CSR).

| Номер бита | Обозначение | Назначение |

| F1 | Код операции | |

| F2 | - // - | |

| F4 | - // - | |

| F8 | - // - | |

| F16 | - // - | |

| I | Управляет сигналом "запрет" - все действия на магистрали запрещены (устанавливается программно) | |

| Dp | Разрешение прерываний (устанавливается программно). Установка значения "1" разрешает контроллеру генерировать запрос на прерывание при появлении хотя бы одного L-запроса | |

| D | Устанавливается контроллером и свидетельствует о том, что какой-то из модулей выставил L-запрос | |

| C | Генерация сигнала "сброс" (устанавливается программно). Установка значения "1" приводит к однократной генерации цикла сброса | |

| Z | Генерация сигнала "подготовка" (устанавливается программно). Установка значения "1" приводит к однократной генерации цикла подготовки | |

| Xp | Разрешение генерации запроса на прерывание по X-ответу модуля (т.е. по X=0) | |

| S | Генерация укороченного цикла магистрали | |

| I* | Индикация состояния линии запрета (устанавливается контроллером) | |

| - | - | |

| X | Отражает состояние линии X (устанавливается контроллером) | |

| Q | Отражает состояние линии Q (устанавливается контроллером) |