Схема работы центнрального процессора

Подмножество кода программы, наиболее «активно» исполняемое в данный отрезок времени, размещено в кэше инструкций (I-кэше). В зависимости от организации процессора инструкции в этом кэше могут храниться в исходном неизменённом виде, либо в частично «предекодированном» виде, либо в полностью «декодированном» виде (то есть в виде готовых МОПов). В случае отсутствия в данном кэше нужных инструкций (исходных либо преобразованных) они считываются из кэша 2-го уровня (L2-кэша), при необходимости подвергаясь предварительному декодированию перед помещением в I-кэш.

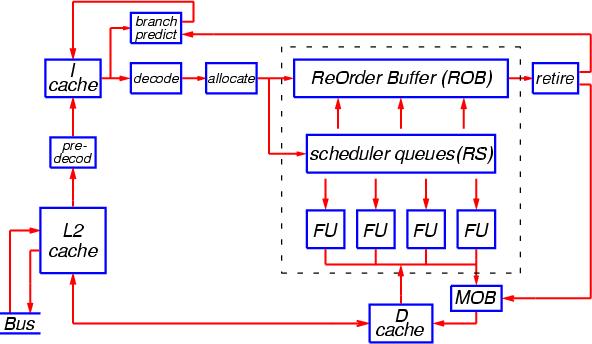

Рис. 2. Структура процессора и взаимодействие его элементов при прохождении машинной инструкции

Инструкции считываются из I-кэша блоками, с опережающей предвыборкой. Текущий блок инструкций отправляется сразу в два устройства – декодер инструкций и предсказатель переходов. Декодер преобразует исходные (либо частично декодированные) инструкции в микрооперации (МОПы), а предсказатель переходов определяет, есть ли в обрабатываемом блоке инструкции перехода, будут ли эти переходы совершены и по каким адресам. Если какой-либо переход предсказывается как «совершённый», то немедленно считывается блок инструкций, находящийся по предсказанному адресу.

Тем временем вновь порождённая декодером группа МОПов поступает в устройство переименования регистров и выделения ресурсов (Rename/Allocate). Переименование (или переназначение) регистров – это выделение данному МОПу нового экземпляра внутреннего регистра процессора, куда будут помещены результаты выполнения этого МОПа. Все дальнейшие операции, зависящие от результатов данного МОПа, будут использовать этот регистр в качестве операнда. «Переименованный» регистр ставится в соответствие регистру, который указан в машинной инструкции (так называемому «архитектурному регистру»). Необходимость в переназначении регистров связана с тем, что архитектурных регистров обычно очень мало, и при использовании столь ограниченного числа регистров невозможно эффективно исполнить поток операций – каждая новая операция, использующая определённый регистр, была бы вынуждена ждать завершения всех предыдущих операций, которые к нему обращаются (даже если ей не нужны результаты этих операций). Наличие большого числа машинных (физических) регистров и механизма переименования позволяет обойти эту проблему. Информация о соответствии регистров хранится в специальных таблицах. В момент отставки МОПа будет произведено обратное преобразование физического регистра в архитектурный.

После преобразования и подготовки регистров поступившая группа МОПов записывается в конец буфера переупорядочения (ReOrder Buffer, ROB). Эта структура является ключевой в организации внеочередного исполнения операций. В ней хранятся все МОПы и необходимые вспомогательные данные от момента завершения декодирования и выделения ресурсов до момента отставки. Таким образом, длина буфера ROB ограничивает число операций, которые одновременно могут находиться в обрабатывающей части процессора (подсистеме внеочередного исполнения) – от самой «старой», которая ещё не завершена и поэтому не может «уйти в отставку», до самой «новой», которая только что поступила из декодера. В случае переполнения буфера переупорядочения, работа декодера приостанавливается до тех пор, пока не произойдёт отставка операций в начале очереди и освобождение места для новых МОПов.

Одновременно с попаданием в ROB новая группа МОПов передаётся в другую структуру данных – пункт резервирования (Reservation Station, RS), откуда МОПы будут отсылаться на исполнение непосредственно в функциональные устройства. Она представляет собой один или несколько буферов, к которым подсоединены эти функциональные устройства. В каждом такте в этих буферах производится поиск операций, которые готовы к исполнению (то есть аргументы которых уже вычислены либо вычисляются и будут готовы к моменту попадания операции в функциональное устройство) вне зависимости от порядка, в котором они записывались в буферы. Устройство, которое осуществляет этот поиск и запуск на исполнение, обычно называют планировщиком, а сами буферы – очередями планировщика. Планировщик отслеживает зависимости между операциями по данным и прогнозирует готовность операций к исполнению в устройствах.

Таким образом, поиск МОПов для внеочередного исполнения всегда производится только в пределах такого буфера планировщика (единого для всех функциональных устройств, либо специфичного для каждой группы устройств), и этот буфер выглядит как «окно», в котором (при необходимости) происходит изменение порядка выполнения операций.

Очередь планировщика представляет собой полностью ассоциативный буфер, с точки зрения поиска операций для исполнения. Но с точки зрения помещения новых МОПов, она ведёт себя как обычная очередь. Все МОПы, находящиеся в какой-то момент в очередях планировщика, одновременно находятся и в буфере ROB. При запуске операции на исполнение в функциональном устройстве соответствующий ей МОП удаляется из очереди планировщика, а в момент завершения операции делается пометка в соответствующем элементе буфера ROB. Когда все МОПы, предшествующие данному, успешно выполнятся и отправятся в отставку, данный МОП также сможет быть отставлен и удалён из буфера ROB. Однако может оказаться, что МОП попал в ошибочную (спекулятивную) ветвь исполнения из-за неверного предсказания перехода — в этом случае вся ветвь будет удалена из буфера переупорядочения после правильного исполнения и отставки данной инструкции перехода.

Когда МОП, запущенный на исполнение в устройстве, удаляется из очереди планировщика, в ней освобождается место для приёма нового МОПа. Это означает, что эффективный размер окна для изменения порядка операций превышает длину данной очереди и ограничивается вместимостью буфера ROB.

К каждой очереди планировщика подсоединено одно или несколько специализированных функциональных устройств. Число операций, которые могут быть запущены на исполнение в каждом такте, обычно заметно превышает ширину остальных трактов процессора и варьируется от 5 (P-III) до 10 (PPC970), что позволяет сглаживать пиковую нагрузку и обеспечить высокую пропускную способность при неоднородной загрузке устройств.

Помимо арифметико-логических и адресных функциональных устройств, в каждом процессоре имеются также устройства загрузки и выгрузки (Load/Store), которые производят доступ к кэшам данных и к оперативной памяти. Эти устройства работают асинхронно от других, и их обычно не изображают на блок-схемах. Логически эти устройства связаны с устройствами вычисления адресов чтения/записи (AGU). Устройства загрузки и выгрузки конвейеризованы и могут одновременно обслуживать большое количество запросов. Эти устройства также осуществляют предварительную выборку из оперативной памяти (копирование в кэши тех данных, использование которых ожидается в ближайшее время). На Рис. 2 группа блоков процессора, образующих подсистему внеочередного исполнения, обведена пунктирной линией.

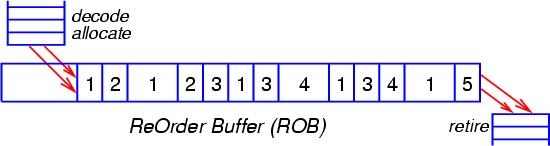

Рис. 3. Различные состояния, в которых могут находиться МОПы, помещённые в буфер переупорядочения.

В хронологическом порядке, каждый МОП может проходить через следующие стадии:

1. находится в очереди планировщика, но ещё не готов к исполнению;

2. готов к исполнению (все аргументы операции вычислены);

3. запущен на исполнение (диспетчеризован);

4. исполнен и ждёт отставки либо отмены спекулятивной ветви;

5. находится в процессе отставки.

Кроме того, в одной микроархитектуре (процессор P-4) перед попаданием в очереди планировщика, приписанные к группам функциональных устройств, все МОПы помещаются в предварительные очереди. Эти очереди выполняют амортизирующую роль, позволяя декодеру и аллокатору осуществлять опережающую подготовку операций.

Может оказаться, что буфер ROB не заполнен до конца – в этом случае в конце буфера (очереди) останется свободное место, куда могут в полном темпе поступать новые МОПы. Для этого необходимо, чтобы в очередях планировщика тоже оставалось свободное место для вновь поступающих МОПов.

Длина буфера переупорядочения в современных процессорах составляет несколько десятков элементов (от 40 в процессоре P-III до 126 в процессоре P-4). В случае если в начале очереди «застрянет» МОП, находящийся в процессе исполнения (например, ожидающий конца медленной операции или прихода данных из памяти), и новые МОПы будут поступать в полном темпе, буфер ROB заполнится за 20-40 тактов (P-III — за 13 тактов). На практике средний темп выполнения операций находится на уровне 50% от предельного или несколько ниже. Взяв такой же темп поступления МОПов, получим время заполнения на уровне 40-80 тактов. Это существенно меньше, чем время ожидания данных из оперативной памяти (200-300 тактов и более). Приведённые цифры показывают, что при большом числе обращений к данным, которых нет в кэшах и для которых не осуществляется эффективная предвыборка, буфер ROB будет, как правило, переполнен, и процессор будет простаивать в ожидании прихода данных из памяти. По существу, в каждый момент времени работу будет блокировать единственный МОП, находящийся в начале очереди и ожидающий загрузки данных. Размер буфера ROB в данном случае определяет, сколько МОПов, расположенных после этого, может быть помещено в ROB и исполнено (при условии, что они не зависят от загружаемых данных) до тех пор, пока процессор не остановится.