Pentium Pro II – два встроенных КЭШ.

L1(встр.)– ёмкость 8 Кб, 4-х строчная, секц-ассоц. – ёмкость 8 Кб, 2-х строчная, секц-ассоц.

L2(внеш.) - ёмкость 256 Кб-1Мб

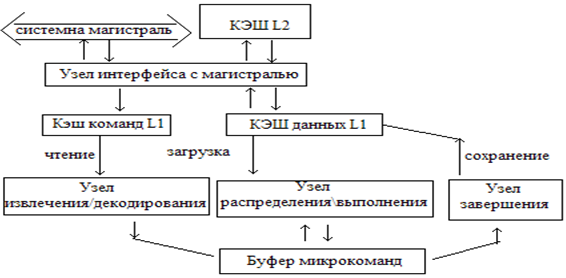

Организация подсистемы КЭШ-памяти

Ядро процессора включает 4 основные узла:

1. Узел извлечения\декодирования – извлекает по порядку команды из КЭШ – команд декодирует, формирует последовательность микроопераций и запоминает их в буфере микрокоманд

2. Буфер микрокоманд – хранит последовательность микрокоманд готовых к выполнению.

3. Распределение\выполнение – планирует выполнение микрокоманд, операций, учитывая их зависимость от данных и доступности необходимых ресурсов.

4. Узел завершения – определяет когда можно будет считать окончательным результат микрооперации и зафиксировать его в КЭШ L1. Этот же узел извлекает из буфера микрокоманд те результаты, выполнение которых уже были зафиксированы и запоминает в КЭШ L1.

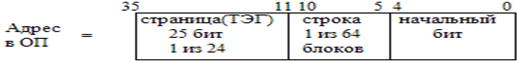

Структура КЭШ-данных

КЭШ-данных разделён на 128 секций по две строки в каждой, таким образом в КЭШ имеется два раздела ёмкостью по 4К. Один раздел объединяет все 0 строки секций, а другой все 1. Каждой строке ставится в соответствие поле тега и два вида состояний. Эти теги и биты объединяются в два массива, так что, в одном массиве имеется один элемент для каждой строки из нулевого раздела, в другом – один элемент из первого раздела.

Для поддержания информационной целостности данных используется метод обратной записи. Но в процессоре Pentium II имеется возможность поменять метод обратной записи на метод сквозной записи. Информационная целостность данных обеспечивает протокол MESI. В соответствии с этим протоколом в КЭШ на каждый ТЭГ имеется два бита, которые несут информацию о текущем состоянии строки: M – изменена (данная строка в КЭШ была изменена, причём эти изменения не отображены в ОП). E – эта строка содержит те же данные, что и соответствующий блок ОП, причем они присутствуют только в данном КЭШ. S– эта строка содержит те же данные, что и блок ОП, причём эти данные присутствуют во всех КЭШ. I – эта строка содержит не обновлённые данные.

Управление КЭШ

Внутренний КЭШ процессора управляет двумя битами одного из управляемых регистров. CD – блокировка КЭШ. NW – запрет сквозной записи

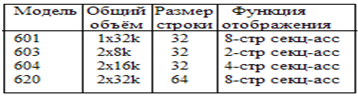

Организации КЭШ в процессоре PowerPC.

В модели G3 объём кэш L1 такой же как в модели G20.

В модели G3 объём кэш L1 такой же как в модели G20.

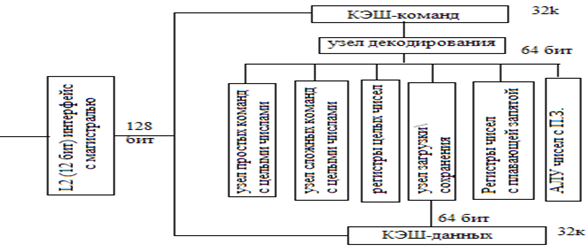

Структурная схема

Два узла могут работать параллельно. КЭШ команд доступен для процессора только в режиме чтения, обеспечивают кодами команд узел декодир. В обоих сегментах уровня L1 в КЭШ-команд и КЭШ-данных имеется ф-я отображения 8 страничная секц-ассоц. Во внутр КЭШ поддержи-ется протокол MESI, во внешнем L2 – 2 страничном, секц-ассоц., объём – 256 к, 512 к, 1 М.

Новые типы динамической памяти: EDRAM, CDRAM, SDRAM, RDRAM, SLDRAM.

Static RAM (SRAM)

Статическая оперативная память

Статическая RAM - наиболее быстрая из доступных на сегодняшний день, она имеет типичное время доступа около 25 наносекунд. Статическая RAM более дорогая и позволяет хранить на чип только четверть от того объёма данных, который может хранить DRAM, так как SRAM использует два транзистора для хранения одного бита против одного у DRAM. В отличие от DRAM, статическая RAM позволяет хранить данные до тех пор, пока на чип подаётся питание. Транзисторы попарно соединены таким образом, что только один из них может быть или включен, или выключен, в то время как другой всегда включен. Синхронная SRAM позволяет более быструю прокачку данных, что необходимо при кэшировании, например, процессоров Pentium 90 или 100 МГц.

Dynamic RAM (DRAM)Динамическая оперативная память

Этот тип физической памяти используется в большинстве персональных компьютеров. Динамическая RAM использует для хранения данных конденсаторы (единичные транзисторы заряжают и разряжают их), которые со временем разряжаются и поэтому требуют постоянной подзарядки для сохранения целостности данных. Это осуществляется таким образом, что между периодами доступа к памяти посылается электрический ток, обновляющий заряд на конденсаторах для поддержания целостности данных, которая не может быть достигнута, если происходит разрядка конденсаторов. Чтение данных из DRAM разряжает конденсаторы, поэтому данные должны быть перезаписаны сразу после чтения.

Термин "динамическая" показывает, что данные в памяти должны постоянно обновляться (перезаряжаться), иначе они будут потеряны. RAM (память со случайным доступом, random-access memory) иногда именуется как DRAM, чтобы отличать её от статической памяти (SRAM). Статическая RAM быстрее и стабильнее, чем динамическая RAM, но потребляет большую мощность и более дорогая.

EDRAM (англ. embedded DRAM — встраиваемая DRAM) — DRAM-память на основе конденсаторов, как правило встраиваемая в тот же самый чип или в ту же самую систему, что и основной ASIC или процессор, в отличие от внешних модулей DRAM и SRAM на основе транзисторов, обычно используемой для кэшей.

Встраивание предусматривает использование более широких шин и более высоких скоростей работы чем при использовании дискретных DRAM модулей. При использовании EDRAM вместо SRAM на чипах, за счет более высокой плотности потенциально может быть реализовано примерно в 3 раза большее количество памяти на той же площади. В силу иной технологии, необходимой для создания памяти DRAM, в производство КМОП-чипов с EDRAM добавляется несколько дополнительных шагов, что удорожает производство.

EDRAM, как и любая другая DRAM память, требует переодического обновления хранящихся данных, что усложняет ее по сравнению с SRAM. Однако, контроллер обновлений EDRAM может быть интегрирован в нее, и тогда чип работает с памятью так же как с SRAM, например такой как 1T-SRAM.

SDRAM (англ. Synchronous Dynamic Random Access Memory) — синхронная динамическая память с произвольным доступом) — тип запоминающего устройства, использующегося в компьютере в качестве ОЗУ.

В отличие от других типов DRAM, использовавших асинхронный обмен данными, ответ на поступивший в устройство управляющий сигнал возвращается не сразу, а лишь при получении следующего тактового сигнала. Тактовые сигналы позволяют организовать работу SDRAM в виде конечного автомата, исполняющего входящие команды. При этом входящие команды могут поступать в виде непрерывного потока, не дожидаясь, пока будет завершено выполнение предыдущих инструкций (конвейерная обработка): сразу после команды записи может поступить следующая команда, не ожидая, когда данные окажутся записаны. Поступление команды чтения приведёт к тому, что на выходе данные появятся спустя некоторое количество тактов — это время называется задержкой (англ. SDRAM latency) и является одной из важных характеристик данного типа устройств

Циклы обновления выполняются сразу для целой строки, в отличие от предыдущих типов DRAM, обновлявших данные по внутреннему счётчику, используя способ обновления по команде CAS перед RAS.

RDRAM — cтандарт оперативной памяти, разработанный компанией Rambus в сотрудничестве с Intel в 1996 году. Высокие частоты памяти обеспечивали 99 % загрузку канала, в то время, когда у конкурирующих стандартов загрузка достигала максимум 70 %. Пропускная способность памяти 1 Гб\с, а позже и фантастические 4 Гб\с.

SLDRAM- разработана для применения в самом широком спектре ПК — от настольных и мобильных компьютеров до высокопроизводительных рабочих станций и серверов. Это достигается благодаря высокой пропускной действительной способности и эффективности, маленьким задержкам, низкому энергопотреблению, легкой возможности наращивания объема и расширяемости (масштабирования) для обеспечения широкой и/или глубокой иерархии конфигурации подсистемы памяти. Микросхема SLDRAM предоставляет собой внутрикристальную конфигурацию множественных независимых логических банков, обеспечивает быстрые циклы обращения шины (Bus Turnaround) при проведении операций чтения/записи и способность работать в полностью конвейеризированном пакетном режиме. АдресацияSLDRAM происходит согласно всем основным требованиям, предъявляемым к динамической памяти в целом, однако имеет довольно серьезные особенности, основанные на полностью пакетном протоколе, что исключает совместимость с любыми другими архитектурами, делая данную уникальной.

Способы защиты памяти.

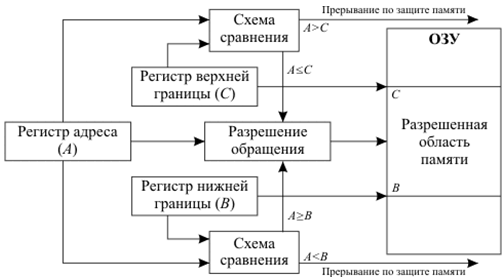

Метод граничных регистров:

Идея метода состоит в том, что вводят два граничных регистра, указывающих верхнюю и нижнюю границы области памяти, куда программа имеет право доступа.

При каждом обращении к памяти проверяется, находится ли используемый адрес в установленных границах. При выходе за границы обращение к памяти подавляется и формируется запрос прерывания, передающий управление операционной системе. Содержание граничных регистров устанавливается операционной системой перед тем, как для очередной целевой программы начнется активный цикл. Если для динамического распределения памяти используется базовый регистр, то он одновременно определяет и нижнюю границу. Верхняя граница подсчитывается операционной системой в соответствии с длиной программы в ОП.

Метод ключей защиты:

Память в логическом отношении делится на блоки. Каждому блоку памяти ставится в соответствие код, называемый ключом защиты памяти. При этом каждой программе, принимающей участие в мультипрограммной обработке, присваивается код ключа программы. Доступ программы к данному блоку памяти для чтения и записи разрешен, если ключи совпадают или один из них имеет код 0.

Метод защиты отдельных ячеек:

В небольших управляющих вычислительных устройствах, работающих, например, в составе АСУ ТП, необходимо обеспечить возможность отладки новых программ параллельно с функционированием находящихся в памяти рабочих программ, управляющих технологическим процессом. Этого можно достичь выделением в каждой ячейке памяти специального разряда защиты. Установка 1 в этот разряд запрещает производить запись в данную ячейку. Это так называемый метод контрольного разряда.

20. Поддержка мультизадачности в микропроцессорах i486+. Исследование сегмента состояния задачи.

В процессорах i486+ поддерживается аппаратные средства мультизадачности. Процедура переключения задач во многом аналогична процедуре прерываний. Мультизадачность однопроцессорной среды реализуется через механизм разделения времени, т.е. каждой задаче выделяется квант времени и создаётся иллюзия параллельности выполняющихся программ. Переключение задач в общем случае похоже на вызовы, но при этом хранится больше информации. Для поддержки мультизадачности в МП i486+ используется: TSS, дескриптор TSS, регистр задач и дескриптор шлюза задач. TSS служит для сохранения информации о задаче. Это сегмент данных для считывания и записи, к которому может обратиться только МП (доступ программы к нему запрещен). TSS определяется дескриптором.

U – User. B – бит занятости (Busy) – активна ли задача в данный момент. Предел ³ 64 Н. DPL определяет того, кто имеет возможность переключения задач (обычно = 0). Дескрипторы TSS размещается только в GDT и выбирается селектором, который находится в регистре TR. Одновременно реализуется одна задача (процесс). Ей соответствует контекст (среда). Специальных команд переключения задач нет. Используются команды межсегментного перехода (JMP) или межсегментного вызова (CALL), а также прерывания, в том числе, особые случаи. JMP и CALL могут быть прямые — сразу с выходом на дескриптор TSS (сегмента состояния задачи) в GDT или косвенные — черезшлюз задачи ШЗ (в IDT). Переключение задач по прерываниям — только косвенное — через ШЗ. Обычный вызов подпрограммы CALL сохраняет содержимое нужных регистров в стеке, программы могут быть реентрантными (обладающими свойством повторной входимости). При переключении задач по CALL создается новая среда, содержимое EFLAGS сохраняется, но не в стеке, а в сегменте TSS. Задачи нереентрантны. Различают два варианта сегмента TSS — 16- и 32-битный. В 16-битном размещается содержимое 8 регистров общего назначения (AX, BX, CX, DX, BP, SP, SI, DI), 4 сегментных регистров (CS, SS, DS, ES), 2 регистров IP, FLAGS, системного регистра LDT (LDTR), селектора адреса возврата («Обратная связь»), 3 пары (SS, SP) для 3 стеков. Три стека используются в связи с четырьмя уровнями (кольцами) привилегий так называемой защиты памяти по привилегиям — 0, 1, 2, 3. Процедура переключения задач («выходящая» задача сменяется «входящей» задачей) связана с изменением содержимого системного регистра TR. Там будет находиться селектор виртуального адреса TSS. Индекс из этого селектора адресует дескриптор TSS (в GDT), сначала старый, потом — новый. Под управлением старого DTSS происходит выгрузка регистрового контекста в сегмент TSS выходящей задачи, а затем — под управлением нового DTSS — загрузка в регистры содержимого соответствующих элементов сегмента TSS входящей задачи. |

21. Поддержка мультизадачности в микропроцессорах i486+. Использование сегмента состояния задачи.

В процессорах i486+ поддерживается аппаратные средства мультизадачности. Процедура переключения задач во многом аналогична процедуре прерываний.

Мультизадачность однопроцессорной среды реализуется через механизм разделения времени, т.е. каждой задаче выделяется квант времени и создаётся иллюзия параллельности выполняющихся программ. Переключение задач в общем случае похоже на вызовы, но при этом хранится больше информации. Для поддержки мультизадачности в МП i486+ используется: TSS, дескриптор TSS, регистр задач и дескриптор шлюза задач. TSS служит для сохранения информации о задаче. Это сегмент данных для считывания и записи, к которому может обратиться только МП (доступ программы к нему запрещен). TSS определяется дескриптором.

| База | U | Предел | Р | DPL | 10B1 | База | |||

| База | Предел | ||||||||

U – User. B – бит занятости (Busy) – активна ли задача в данный момент. Предел 64 Н. DPL определяет того, кто имеет возможность переключения задач (обычно = 0). Дескрипторы TSS размещается только в GDT и выбирается селектором, который находится в регистре TR.

Одновременно реализуется одна задача (процесс). Ей соответствует контекст (среда). Специальных команд переключения задач нет. Используются команды межсегментного перехода (JMP) или межсегментного вызова (CALL), а также прерывания, в том числе, особые случаи. JMP и CALL могут быть прямые — сразу с выходом на дескриптор TSS(сегмента состояния задачи) в GDT или косвенные — черезшлюз задачи ШЗ (в IDT). Переключение задач по прерываниям — только косвенное — через ШЗ. Обычный вызов подпрограммы CALL сохраняет содержимое нужных регистров в стеке, программы могут быть реентрантными (обладающими свойством повторной входимости). При переключении задач поCALL создается новая среда, содержимое EFLAGS сохраняется, но не в стеке, а в сегменте TSS. Задачи нереентрантны.

Различают два варианта сегмента TSS — 16- и 32-битный. В 16-битном размещается содержимое 8 регистров общего назначения (AX, BX, CX, DX, BP, SP, SI, DI), 4 сегментных регистров (CS, SS, DS, ES), 2 регистров IP, FLAGS, системного регистра LDT (LDTR), селектора адреса возврата («Обратная связь»), 3 пары (SS, SP) для 3 стеков. Три стека используются в связи с четырьмя уровнями (кольцами) привилегий так называемой защиты памяти по привилегиям — 0, 1, 2, 3.

Процедура переключения задач («выходящая» задача сменяется «входящей» задачей) связана с изменением содержимого системного регистра TR. Там будет находиться селектор виртуального адреса TSS. Индекс из этого селектора адресует дескриптор TSS (в GDT), сначала старый, потом — новый. Под управлением старого DTSS происходит выгрузка регистрового контекста в сегмент TSS выходящей задачи, а затем — под управлением нового DTSS — загрузка в регистры содержимого соответствующих элементов сегмента TSS входящей задачи.