Организация системы шин L, S, X и M в компьютере РС/АТ

Следует отметить, что описанная выше система из одной, разбитой на три секции, шины, использовалась лишь в древних ЭВМ класса IBM PC XT. Имея название “Общая шина”, она и впрямь пронизывала весь компьютер, позволяя соединить в каждый момент времени процессор с одним из приборов памяти либо одним из контроллеров периферийных устройств. На самом деле в нашем компьютере имеется не одна, а несколько шин (см.рис.2.2). Основных шин четыре, и обозначаются они как L-шина, S-шина, М-шина и X-шина. Нами только что рассматривалась L-шина (или локальная шина), линии адреса и данных которой связаны непосредственно с микропроцессором. Можно ввести понятие удаленности шины от процессора, считая, что чем больше буферов отделяют шину, тем она более удалена от процессора. Тогда L-шина может считаться ближайшей к процессору.

Рис 2.2. Шинная организация IBM PC AT

Основной шиной, связывающей компьютер в единое целое, является S-шина, или системная шина, к которой, кроме того, подключаются адаптеры периферийных устройств, не входящих в состав системного ядра. Именно она выведена на 8 специальных разъемов-слотов. Эти слоты хорошо видны на системной плате компьютера: в них установлены платы периферийных адаптеров (дисплея, флоппи-диска, винчестера, мыши и т.д.).

При переходе с шины L на шину S сигналы процессора должны претерпеть определенную трансформацию. В частности, максимальная нагрузочная способность линий микропроцессора не превышает одного TTL входа, так как максимальный выходной ток этих линий не должен превышать 1мА. Поэтому между линиями L - шины и S - шины должны располагаться буферные элементы, повышающие мощность выводов как минимум в сто раз. Кроме того, шина данных микропроцессора, как мы увидим в дальнейшем, не всегда должны соединяться с остальными частями ЭВМ. При выполнении так называемого внепроцессорного обмена микропроцессор вообще должен быть отключен от остальных схем компьютера.

Защелкивание (этот распространенный в среде инженеров - электронщиков термин обозначает сохранение информации в регистре) кода адреса необходимо по следующей причине. К тому моменту, когда на шинах данных появляется информация, подлежащая перемещению в микропроцессор или из него, должен уже быть подготовлен тракт передачи этой информации от источника к приемнику, проходящий через систему шин и образованный целым набором буферных усилителей и шинных формирователей. Как известно, переключение выводов микросхем из высокоимпедансного состояния в рабочее, а также переключение направления передачи информации требует определенного времени. Кроме того, время затрачивается на дешифрацию элементов, участвующих в данном обмене. Следовательно, адресная информация должна быть выставлена на шину заблаговременно - еще в конце машинного цикла, предшествующего циклу рассматриваемого обмена, и сохраняться в регистре. Кроме того, для максимально возможного увеличения скорости обмена адресная информация, необходимая для дешифрации периферийных микросхем, вообще фиксируется и участвует в подготовке обмена начиная примерно с середины предыдущего цикла. Этот вариант адреса, образующийся на линиях LA(17) - LA(23), и соответствующий адресу обмена в следующем цикле, меняется уже тогда, когда на остальных линиях адреса системной шины еще присутствует информация, соответствующая адресу обмена в текущем цикле.

Эволюция шинной архитектуры

Когда микропроцессор с рассмотренной шинной архитектурой выполняет, например, команду чтения из памяти, воздействие (адрес и сигналы управления) с локальной L шины попадает на системную S шину, а только затем на шину памяти M. После этого данные, считанные из памяти, опять-таки попадают на системную шину, а с нее - на локальную. Очевидно, что каждый перенос информации через тот или иной буферный элемент сопровождается определенной задержкой. И пусть одна задержка невелика (не более 10 наносекунд), но суммарно их набирается довольно много, что и определяет ту довольно низкую тактовую частоту, на которой работали первые IBM PC - 12, или даже 8 Мгц.

Рис 2.3 Классическая архитектура IBM PC AT 286

Для устранения таких потерь в более поздних моделях IBM PC AT 286 основная оперативная память выделяется в особую подсистему и доступ к ней осуществляется не через системную шину, а параллельно с доступом к системной шине. Как правило, это связано с наличием интегрированного контроллера шины данных. Суммарная задержка передачи данных в этом случае сокращается примерно до 20 нс, а тактовая частота повышается до 25 МГц.

Рис 2.4 Архитектура IBM PC AT 286 поздних моделей

Дальнейшее совершенствование систем в этом направлении привело к тому, что переход от шины данных LD локальной шины к шине MD шины памяти упростился до предела. Функцию контроллера шины данных в этом случае выполняет обычный шинный формирователь. На первый взгляд, в нем нет необходимости и можно было бы просто объединить шины LD и MD. Но по соображениям согласования электрических сигналов этого нельзя делать.

Рис 2.5 Архитектура IBM PC AT 386 с конвертором системной шины

Дальнейшие возможности повышения производительности процессора связаны с поисками решений в области архитектуры РС АТ. Введение кэш- памяти позволило ослабить требования по времени доступа к основной оперативной памяти (кэш-память - это статическая память с малым временем доступа, которая не “видна” для программного обеспечения. Объем ее колеблется от 128Кбайт до 1 Мбайт). При этом на локальной шине, кроме микропроцессора и сопроцессора, появляется контроллер управления кэш- памятью. При объеме памяти 128 Кбайт вероятность того, что необходимая микропроцессору информация окажется в кэш-памяти, состовляет 95-98%. Эффективность кэш-памяти становится значительной на частотах выше 20 Мгц, так как в этом случае потери производительности из-за задержек доступа к оперативной памяти очень чувствительны.

Последующие архитектурные изменения связаны с переходом от процессоров, имеющих 32 разрядные шины данных (i80386 и i80486), к процессорам, имеющим 64 разрядные шины, а именно к процессорам Pentium, Pentium Pro и Pentium II.

Рис 2.6 Архитектура IBM PC AT с кеш-памятью

Передача информации в МПС

При организации последовательного обмена ключевыми могут считаться две проблемы:

1) синхронизацию битов передатчика и приемника;

2) фиксацию начала сеанса передачи.

В МПС существует три способа передачи информации:

· асинхронный;

· синхронный;

· смешанный.

Асинхронный способ характеризуется тем, что сигналы передаются с произвольными промежутками времени.

Синхронный способ характеризуется тем, что сигналы передаются строго периодично во времени.

Смешанный способ характеризуется тем, что байты передаются асинхронно, а биты внутри байтов синхронно.

Асинхронный способ

Асинхронный способ обеспечивает передачу информации по единственной линии. Для надежной синхронизации обмена в асинхронном режиме

1) передатчик и приемник настраивают на работу с одинаковой частотой;

2) передатчик формирует стартовый и стоповый биты, отмечающие начало и конец посылки;

3) передача ведется короткими посылками (5..9 бит), а частоты передачи выбираются сравнительно низкими.

Асинхронный способ по методу регистрации сигналов делится на:

· стробируемый;

· «запрос-ответ».

Метод стробирования

Строб – дополнительный сигнал, является подтверждением действительности других сигналов.

Стробирование может осуществляться по фронту или по уровню.

Рис. 3.1 Виды стробов.

рис 3.2 Стробируемый метод

рис 3.3 Стробируемый метод

Стробирование по фронту.

Достоинства:

· легкая аппаратная реализация;

· высокое быстродействие.

Недостатки:

· нельзя использовать строб сигнал как сигнал синхронизации;

· момент переключения трудно зафиксировать программно.

Стробирование по уровню.

Достоинства:

· легкая аппаратная реализация;

· легкая программная реализация;

· легкая организация приема от нескольких источников.

Недостатки:

· нельзя использовать строб сигнал как сигнал синхронизации;

· меньшее быстродействие.

Метод «запрос-ответ»

рис 3.4 Метод «запрос-ответ»

t1 – передатчик выставляет данные (предварительно проверив отсутствие строба-ответа)

t2 – передатчик с некоторой задержкой выставляет сигнал строб-запрос

t3 – приемник, анализируя состояние линии строб-запрос, обнаруживает наличие определенного сигнала и в этот же момент осуществляет прием данных по линии.

t4 – передатчик, сканируя линию строб-ответ, обнаруживает, что он активен и сбрасывает строб-запрос

t5 – приемник, сканируя линию строб-запрос, обнаруживает, что строб запрос стал неактивен и сбрасывает строб-ответ

t6 – тоже самое, что и t1

Достоинства:

· позволяет сопрягать аппаратуру существенно отличающуюся быстродействием;

· легко организуется программным путем.

Недостатки:

· нельзя использовать строб сигнал как сигнал синхронизации;

· меньшее быстродействие.

Синхронный способ

В синхронном способе передачи информации выделяют изохронный метод.

Синхронизация бывает:

· внутренняя

· внешняя

Изохронный метод

В этом методе передачи информации возможна потеря данных. Здесь сам приемник определяет какие данные принимать, а какие нет (например для звуковой информации).

Внешняя синхронизация

Сигналы синхронизации поступают вместе с данными. В этом случае форма сигналов может быть неправильной. Поэтому внешняя синхронизация используется только при передаче на небольшие расстояния, т.е. внутри платы.

Внутренняя синхронизация

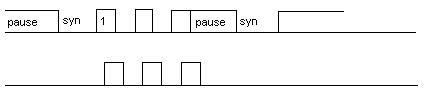

рис 3.5 Внутренняя синхронизация

SYN – специальный сигнал пересылаемый один раз и запускающий тактовый генератор.

Достоинства:

· достаточно двух линий: сигнал и земля;

· высокая частота;

· высокая надежность связи;

· длина пакета определяется взаимной синхронностью передатчики и приемника.

|

При синхронном методе передатчик генерирует две последовательности - информационную TxD и синхроимпульсы CLK, которые передаются на приемник по разным линиям (Рис. 3.6).

Рис. 3.6. Последовательный синхронный обмен с внешней синхронизацией

Синхроимпульсы обеспечивают синхронизацию передаваемых бит, а начало передачи отмечается по-разному.

При организации внешней синхронизации сигнал начала передачи BD генерируется передатчиком и передается на приемник по специальной линии (Рис. 3.6).

В системах с внутренней синхронизацией отсутствует линия BD, а на линию данных генерируются специальные коды длиной 1-2 байта - “символы синхронизации”. Для каждого приемника предварительно определяются конкретные синхросимволы, таким образом можно осуществлять адресацию конкретного абонента из нескольких, работающих на одной линии. Каждый приемник постоянно принимает биты с RxD, формирует символы и сравнивает с собственными синхросимволами. При совпадении синхросимволов последующие биты поступают в канал данных приемника.