Типовые последовательные схемы

Триггеры

Триггеры представляют собой простейшие последовательные устройства (автоматы). Они широко используются в узлах электронной аппаратуры в виде самостоятельных элементов или в качестве базовых элементов для построения других, более сложных приборов (счетчиков, регистров, запоминающих устройств).

К триггерам относят большой класс устройств, общим свойством которых является способность длительно оставаться в одном из двух (или нескольких) возможных устойчивых состояний и скачком чередовать их под воздействием внешних сигналов. Значения выходных сигналов зависят не только от значений входных сигналов, но и от последовательности их изменений. Каждое состояние легко распознается по значению выходных напряжений и триггеров – запоминание информации. Под памятью триггера подразумевается способность оставаться в заданном состоянии и после прекращения действия переключающего сигнала. Приняв одно из состояний за 1, а другое – за 0, можно считать, что триггер хранит (помнит) один разряд числа в двоичном коде.

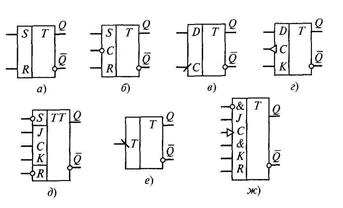

Рис. 55. Условные обозначения триггеров: асинхронный RS-триггер (а);

синхронный RS-триггер (б); D-триггер (в); JK-триггер (г);

двухступенчатый JK-триггер (д); Т-триггер, срабатывающий по срезу (е);

JK-триггер с логическими элементами & на входах J и K (ж)

Понятие «триггер» охватывает много видов устройств, которые существенно различаются между собой по выполняемым функциям, схемному исполнению, способам управления, электрическим и конструктивным параметрам.

Для рассмотрения последовательных схем требуется введение в явном виде времени для описания изменений потенциальных сигналов. Аналитически это можно сделать с помощью операторов переходов d и  .

.

Потенциальные (асинхронные) и импульсные сигналы. Сигналы называются потенциальными, если интервалы времени Тi между соседними изменениями сигналов значительно больше времени реакции схемы τP, в которой они используются, т.е. сигнал x(t) будет потенциальным, если min (T1, T2, T3) >> τP. Сигнал называется импульсным, если его длительность того же порядка, что и время реакции схемы (схема должна отреагировать на воздействие импульсного сигнала, а импульсный сигнал должен закончиться сразу же после окончания переходного процесса). При аналитическом описании схем, на которые воздействуют импульсные сигналы, используется понятие абстрактного импульсного сигнала, длительность которого бесконечно мала. Такие сигналы (dx,  , ∆x) порождаются изменениями сигнала x с 1 на 0 и с 0 на 1. Реальные импульсные сигналы всегда имеют конечную длительность, которая определяется временем реакции схемы и может изменяться в широких пределах в зависимости от быстродействия ЛЭ, на которых она построена. Понятие абстрактного импульсного сигнала позволяет абстрагироваться от физических параметров схемы.

, ∆x) порождаются изменениями сигнала x с 1 на 0 и с 0 на 1. Реальные импульсные сигналы всегда имеют конечную длительность, которая определяется временем реакции схемы и может изменяться в широких пределах в зависимости от быстродействия ЛЭ, на которых она построена. Понятие абстрактного импульсного сигнала позволяет абстрагироваться от физических параметров схемы.

Оператор перехода d определяется соотношением

dx =  ·x(t –∆t),

·x(t –∆t),

где dx – импульсный сигнал, порождаемый изменениями потенциального сигнала с 1 на 0; x(t) – значение потенциального сигнала в данный момент времени; x(t – ∆t) – значение потенциального сигнала в предыдущий момент времени. Очевидно, dx = 1 только при изменении потенциального сигнала x с 1 на 0.

Ценность соотношения заключается в том, что оно учитывает в явном виде время и может использоваться не только для потенциальных сигналов, но и для переключательных функций от потенциальных сигналов.

Асинхронные потенциальные триггеры (триггерные ячейки)

В простейшем исполнении триггер представляет собой симметричную структуру из двух логических элементов: ИЛИ – НЕ либо И – НЕ, охваченных перекрестной положительной связью. Такие триггеры называются симметричными. Схема симметричного триггера на основе логических элементов

«И – НЕ» дана на рис. 56, а. Этот триггер (бистабильная ячейка, ячейка памяти, асинхронный RS-триггер) обладает двумя устойчивыми состояниями, которые обеспечиваются за счет связи выхода каждого элемента с одним из входов другого. Свободные входы служат для управления и называются информационными или логическими.

Симметрия схемы не означает симметрии электрических режимов обоих каскадов. За счет перекрестного соединения входов создаются условия, при которых при отсутствии входных сигналов один из логических элементов будет заперт, а другой – открыт.

Одному из выходов триггера присваивают наименование прямого (в силу симметрии схемы им может быть любой) и обозначают символом Q, а другому – наименование инверсного и обозначают  , что в логическом смысле означает, что сигнал на этом выходе противоположен первому. Состояние триггера отождествляют с сигналом на прямом выходе, т.е. триггер находится в единичном состоянии, когда Q = 1, а

, что в логическом смысле означает, что сигнал на этом выходе противоположен первому. Состояние триггера отождествляют с сигналом на прямом выходе, т.е. триггер находится в единичном состоянии, когда Q = 1, а  = 0, и в нулевом, когда

= 0, и в нулевом, когда  Q = 0, а

Q = 0, а  = 1.

= 1.

Смена состояний триггера производится внешними сигналами. Название этого процесса имеет много синонимов: переключение, опрокидывание, переброс, запись информации. Начало опрокидывания происходит с приходом отрицательного перепада напряжения – (0) на вход закрытого элемента. Вход, по которому триггер устанавливается в единичное состояние (Q = 1,  = 0), называют входом S (от англ. set – установка), а в нулевое (Q = 0,

= 0), называют входом S (от англ. set – установка), а в нулевое (Q = 0,  = 1) – вход R (reset – возврат).

= 1) – вход R (reset – возврат).

а) б) в)

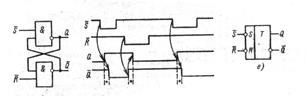

Рис. 56. Схема RS-триггера на ЛЭ «И – НЕ» (а);

диаграмма переключений (б); условное обозначение (в)

Карта Карно (рис. 57), отображающая функции состояний входов и выхода RS – триггера «И – НЕ». Ф – фиктивное, запрещенное состояние, характеризующее свойство триггера, имеющего только два устойчивых состояния, способных хранить 1 бит информации (данных).

Рис. 57

Таблица 1

Функциональное назначение входов триггеров

| Условное обозначение | Наименование |

| Информационные входы | |

| S | Вход раздельной установки триггера в состояние 1 |

| R | Вход раздельной установки триггера в состояние 0 |

| J | Вход установки JK-триггера в состояние 1 |

| K | Вход установки JK-триггера в состояние 0 |

| T | Вход счетного триггера (счетный вход) |

| D | Вход установки D-триггера в состояние 1 |

| Управляющие входы | |

| V | Подготовительный вход разрешения приема информации |

| C | Исполнительный вход приема информации, вход синхронизации (тактовый вход) |