С помощью сигнатур

В данном разделе более детально рассматривается реализация метода блокового контроля с помощью сигнатур. В качестве конкретного микропроцессора выбран микроконтроллер 1816ВЕ51. Рассматриваемый метод блокового контроля правильности хода выполнения программы (функциональной модели МП системы) основан на сравнении в конце выделенного блока команд эталонной сигнатуры с вычисляемой сигнатурой. Сигнатура в нашем случае – результат поразрядного сложения по модулю два байтов команд на шине данных, выполняемых по разомкнутому пути программы (блоку программы). Программа должна быть написана так, чтобы в конце оцениваемого пути сигнатура равнялась нулю. СВК фиксирует сигнал конца блока и сравнивает накопленную сигнатуру с нулем. Сигнал конца блока формируется СВК при выполнении команды

LCALL AC,

т.е. вызов подпрограммы по адресу, указанному во втором и третьем байтах команды, где АC – выделенные для СВК адреса из адресного пространства ПЗУ. СВК выделяет момент появления АC на адресной шине и стробирует сигнатуратор. По адресу АC в ПЗУ хранится команда RET (возврат из подпрограммы).

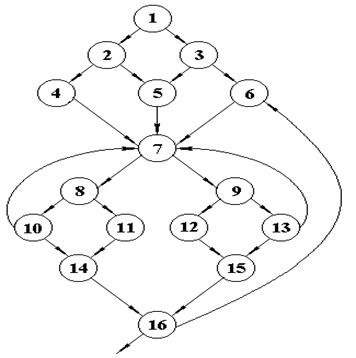

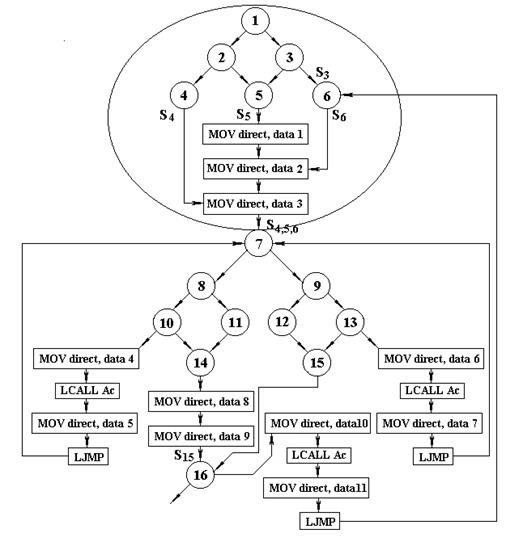

Рассмотрим пример. На рис. 4.45 приведена граф-схема фрагмента программы, где вершины соответствуют линейным участкам программы (в частном случае – одной команде), а на рис. 4.46 показана граф-схема этой программы с дополнительными командами, обеспечивающими равенство сигнатуры нулю в точках сравнения или требуемые значения в точках схождения и замыкания контуров (S4,5,6; S14,15; S3).

Рис.4.45.Граф-схема фрагмента программы Рис.4.45.Граф-схема фрагмента программы |

Выравнивание сигнатур выполняется при помощи команды

MOV direct,#data

Поле direct фиксировано и определяет адрес ячейки внутреннего ОЗУ, не используемой в рабочей программе. Меняя поле #data, можно добиться требуемого значения сигнатуры. Если значение поля direct принять равным коду команды, то сумма по модулю два кода команды и поля direct равна нулю. В этом случае, чтобы после выполнения выравнивающей команды сигнатура стала равной нулю, поле #data должно принять значение эталонной сигнатуры, полученное до выполнения этой команды.

Рассмотрим выделенный окружностью участок программы на рис. 4.46 (см. ниже). Пусть S4, S5, S6 – сигнатуры, вычисленные к моменту выполнения команд выравнивания по соответствующим путям. Пусть к моменту выполнения фазы 7 сигнатура S4,5,6 должна равняться нулю, независимо от того, по какому пути выполнился переход к 7.

Определим data 1, data 2, data 3:

S4 + data 3 = 0, отсюда data 3 = S4;

S6 + data 2 + data 3 = 0, отсюда data 2 = S6 + S4;

S5 + data 1 + data 2 + data 3 = 0, отсюда data 1 = S5 + S6.

В случае прерывания программ необходимо запомнить сформированную сигнатуру в стеке, а после завершения подпрограммы обработки прерывания – восстановить ее в сигнатураторе. Предлагается организовать стек в ОЗУ ЦП. Первые команды подпрограммы обработки прерывания должны обеспечить ввод в стек текущей сигнатуры с учетом сигнатуры команд, выполняющих ввод в стек.

Оценим объем дополнительной памяти (М) для команд, обеспечивающих реализацию рассматриваемого метода контроля. Пусть D – число команд, на которые выполняется переход больше чем из одного места программы (узловые команды), Si – число переходов к i-й узловой команде, С – число циклов в программе. Все команды, используемые для модификации программы, трехбайтные.

Рис. 4.46. Граф-схема программы с дополнительными командами Рис. 4.46. Граф-схема программы с дополнительными командами |

Каждое сравнение сигнатуры с 0 требует выполнения трех команд:

MOV direct, #data – обеспечивает нулевую сигнатуру;

LCALL AC – инициирует момент сравнения;

LJMP – обеспечивает продолжение рабочей программы.

Таким образом,

.

.

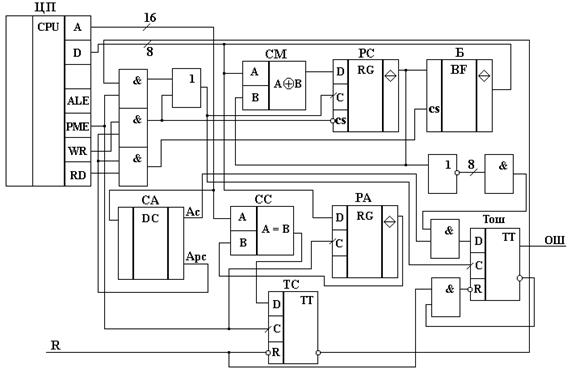

На рис. 4.47 приведена функциональная схема СВК, реализующая рассматриваемый блоковый метод контроля правильности хода выполнения программы для однокристального микроконтроллера 1816ВЕ51 как объекта контроля. Сигналы с шины данных ЦП поступают на первый вход, а сигналы из регистра сигнатуры (РгС) – на второй вход сумматора по mod2 (СМ). Результат сложения фиксируется по фронту сигнала РМЕ ЦП в РС. Содержимое РС может быть записано в ЦП через буфер Б или загружено из ЦП при выполнении команды MOV X. Для этого РС присваивается адрес Арс из адресного пространства внешнего ОЗУ. При загрузке РС переводится в третье состояние, это обеспечивает на втором входе сумматора все единицы и РгС < – D + 1...1.

Рис. 4.47. Функциональная СВК, реализующая блоковый метод контроля Рис. 4.47. Функциональная СВК, реализующая блоковый метод контроля |

Обращение к ПЗУ по адресу Ас вызывает стробирование схемы сравнения содержимого РгС с О (ССО), и триггер ошибки (Тош) формирует сигнал ошибки (Ош) в виде короткого импульса, если результат не равен нулю. Селектор адреса (СА) распознает адреса Ас и Арс. В микроконтроллере 1816ВЕ51 в машинном цикле всегда происходит два обращения к ПЗУ программ. Для однобайтной команды, например, при втором обращении к ПЗУ будет выбран следующий байт, но на выполнение текущей команды он не повлияет. Этот байт будет выбран снова при выборке следующей команды. Таким образом, возможна ситуация выборки из ПЗУ дважды подряд по одному и тому же адресу. Предположим, что из-за дефекта в некоторой ячейке ПЗУ произошло изменение содержимого. Обращение два раза подряд к одной и той же ячейке ПЗУ добавляет к сигнатуре 0. Нуль получается как в случае исправности, так и в случае неисправности, т.е. СП не обнаруживает большую часть дефектов ПЗУ, нарушающих механизмы хранения и выборки. Для исключения этой ситуации СП не должен добавлять к сигнатуре код, полученный при повторном обращении к ячейке ПЗУ. Это достигается следующим образом. Вводится регистр адреса РА, фиксирующий по фронту сигнала РМЕ состояние адресной шины. Схема совпадения (СС) определяет, является ли текущий адрес таким же, как при предыдущем обращении к ПЗУ, сравнением состояний РА и шины А. Результат сравнения фиксируется в триггере ТС по срезу сигнала РМЕ. В случае совпадения ТС блокирует прохождение сигнала РМЕ на синхровход РгС.