Структурная схема процессора

Содержание

1. Постановка задачи….………………………………………………………………………3

2. Определение форматов команд и их кодировка….……………………………………..4

3. Структурная схема процессора………………….………………………………………..6

4. Разработка блока арифметико-логического устройства (АЛУ) ………………………..7

5. Разработка блока регистров (БР)…. ……………………………………………………..10

6. Разработка устройства управления (УУ)…...……………………………………………11

7. Разработка формата микрокоманд. Микрокод….……………………………………….14

8. Кодировка микрокоманд…………………………………………………………………..16

8. Примеры программ…………………..……………………………………………………17

9. Оценка производительности и сложности процессора………………………………....19

Постановка задачи

Синтезировать структуру простого магистрального процессора с одним АЛУ, выполняющего 8 заданных команд. Разработать формат команд, кодировку команд. Разработать структурную схему процессора, функциональные схемы всех блоков процессора, функциональную схему процессора в целом с указанием всех шин и управляющих сигналов. Разработать формат микрокоманд, организацию управления всеми устройствами процессора, микрокод для каждой из заданных команд. Привести примеры выполнения каждой команды с указанием значения всех основных сигналов и содержимого основных регистров на каждом такте. Привести 2 примера небольших программ с указанием значения основных сигналов и содержимого основных регистров на каждом такте.

Определить максимальную тактовую частоту процессора. Определить производительность процессора в операциях в секунду (IPS), а также выраженную в числе выполняемых тестовых программ в секунду. Указать способы повышения производительности процессора.

Характеристика процессора: простой процессор магистрального типа с одноблочным универсальным АЛУ. Разрядность регистров РОН и АЛУ процессора – 8 бит. Число РОН – 4. Адресуемая память - 256 слов (байт). Устройство управления – микропрограммное с ПЗУ микропрограмм. Способ выполнения команд – последовательное выполнение. Адресация памяти – прямая.

Особенности АЛУ:

Тип сдвигателя – комбинационный на любое число разрядов в одну сторону.

Адресность команд – трёхадресные (типа add r1, r2, r3).

Адресная арифметика – на отдельном АЛУ.

Операции АЛУ:

· ADD – сложение;

· SHR – сдвиг вправо логический;

· NOR – ИЛИ-НЕ;

· EQU – проверка на равенство.

Особенности УУ:

Варианты адресации – регистровая, прямая, косвенная регистровая, косвенная регистровая по базе.

Логика обработки команд – комбинационная

Выполняемые команды:

· LD – загрузка из памяти;

· ST – сохранить в память;

· ADD – сложение;

· SHR – сдвиг вправо логический;

· JE – переход по нулю;

· NOR – ИЛИ-НЕ;

· JMP – безусловный переход;

· XCH – обмен регистров.

Ограничения на формат и загрузку команд:команды, имеющие разную длину, не выравниваются до максимальной длины, команды считываются по 8-разрядной шине данных памяти за разное количество шагов.

Не декодировать разные форматы в разные адреса!!!

Определение форматов команд и их кодировка

Необходимо реализовать 8 различных команд. Для кодирования 8 различных команд потребуется 3 бита кода команды (КК). Выберем следующие коды команд:

| КОП | Команда | Описание |

| LD Rx, adr LD Rx,[Ry] LD Rx,[Ry],[Rz] | Загрузить в регистр | |

| ST Rx, adr ST Rx,[Ry] ST Rx,[Ry],[Rz] | Сохранить из регистра в адрес adr | |

| ADD Rx, Ry, Rz | Rx=Ry+Rz Записывает результат сложения второго и третьего операнда в первый операнд | |

| NOR Rx, Ry, Rz | Rx = !(Ry || Rz) Или-Не | |

| SHRA Rx, Ry,Rz | Rx = Ry/2*Rz Арифметический сдвиг вправо | |

| XCH Rx, Ry | Обмен Rx ó Ry | |

| JE Rx, Ry, adr | Переход при равенстве Rx==Ry по адресу adr | |

| JMP adr | Переход безусловный по адресу adr |

Способы адресации:

| Способ адресации(СА) | Код |

| Прямая | |

| Регистровая | |

| Косвенная регистровая | |

| Косвенная регистровая по базе (индексная) |

Здесь Rx, Ry, Rz – регистры из числа РОН, (могут повторяться); adr – адрес памяти.

Форматы команд:

| LD Rx, adr | |||||||||||||||||||||||

| Код | Rx | Ry | Rz | Сп. адр | Не используется | Адрес | |||||||||||||||||

| X | X | - | - | - | - | - | - | - | - | - | a7 | a6 | a5 | a4 | a3 | a2 | a1 | a0 | |||||

| LD Rx,[Ry] | |||||||||||||||||||||||

| Код | Rx | Ry | Rz | Сп. адр | Не используется | Адрес | |||||||||||||||||

| X | X | Y | Y | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | |||||

| LD Rx,[Ry],[Rz] | |||||||||||||||||||||||

| Код | Rx | Ry | Rz | Сп. адр | Не используется | Адрес | |||||||||||||||||

| X | X | Y | Y | Z | Z | - | - | - | - | - | - | - | - | - | - | - | - | - | |||||

| ST Rx, adr | |||||||||||||||||||||||

| Код | Rx | Ry | Rz | Сп. адр | Не используется | Адрес | |||||||||||||||||

| X | X | - | - | - | - | - | - | - | - | - | a7 | a6 | a5 | a4 | a3 | a2 | a1 | a0 | |||||

| ST Rx,[Ry] | |||||||||||||||||||||||

| Код | Rx | Ry | Rz | Сп. адр | Не используется | Адрес | |||||||||||||||||

| X | X | Y | Y | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | |||||

| ST Rx,[Ry],[Rz] | |||||||||||||||||||||||

| Код | Rx | Ry | Rz | Сп. адр | Не используется | Адрес | |||||||||||||||||

| X | X | Y | Y | Z | Z | - | - | - | - | - | - | - | - | - | - | - | - | - | |||||

| ADD Rx, Ry, Rz | |||||||||||||||||||||||

| Код | Rx | Ry | Rz | Сп. адр | Не используется | Адрес | |||||||||||||||||

| X | X | Y | Y | Z | Z | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | |||

| NOR Rx, Ry, Rz | |||||||||||||||||||||||

| Код | Rx | Ry | Rz | Сп. адр | Не используется | Адрес | |||||||||||||||||

| X | X | Y | Y | Z | Z | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | |||

| SHRA Rx, Ry, Rz | |||||||||||||||||||||||

| Код | Rx | Ry | Rz | Сп. адр | Не используется | Адрес | |||||||||||||||||

| X | X | Y | Y | Z | Z | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | |||

| XCH Rx, Ryz | |||||||||||||||||||||||

| Код | Rx | Ry | Rz | Сп. адр | Не используется | Адрес | |||||||||||||||||

| X | X | Y | Y | Z | Z | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | |||

| JMP adr | |||||||||||||||||||||||

| Код | Rx | Ry | Rz | Сп. адр | Не используется | Адрес (adr) | |||||||||||||||||

| - | - | - | - | - | - | - | - | - | - | - | - | - | a7 | a6 | a5 | a4 | a3 | a2 | a1 | a0 | |||

Структурная схема процессора

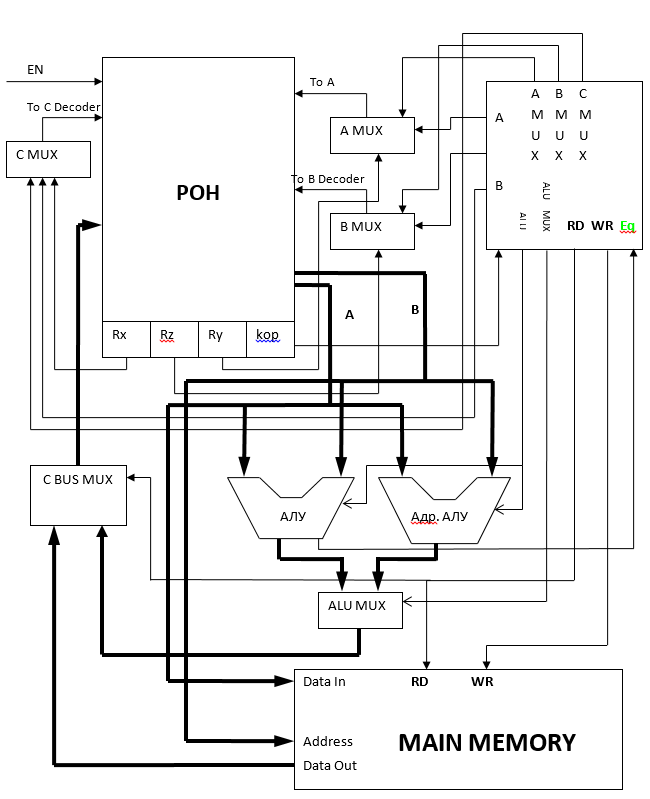

Рис. 1. Структурная схема процессора

АЛУ соединено двумя шинами (А и В) с блоком РОН для выборки операндов в командах. Выход результата работы блока АЛУ осуществляется по одной шине С, которая связана с блоком РОН для записи результата. Поскольку запись в РОН может происходить как с выхода АЛУ, так и из памяти, то необходимо предусмотреть мультиплексор шины C.

Адрес следующей команды находится в регистре PC (Program Counter) процессора. Он относится к управляющим регистрам процессора. Регистр PC выводит адрес на шину адреса процессора, как отмечалось выше, в данном случае разрядность шины выбрана равной 8 битам. После выполнения обычных команд PC увеличивается на единицу, а при выполнении условных команд (JE и JMP) он может перезаписываться адресом, указанным в команде.

Следующая выполняемая команда загружается в регистр команд IR и хранится там до загрузки очередной. Регистр команд связан с блоком управления (с него поступает код команды), с блоком РОН (так как в команде закодированы регистры-операнды, со входом регистра PC, с мультиплексором на шине А, B, C и с мультиплексором на шине данных Main Memory.