Б2В Сегментная схема функционирования виртуальной оперативной памяти

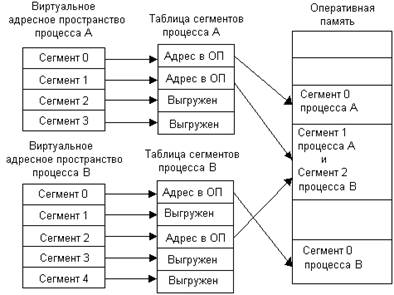

Сегментное распределение виртуальное адресное пространство процесса делится на части — сегменты, размер которых определяется с учетом смыслового значения содержащейся в них информации. Отдельный сегмент может представлять собой подпрограмму, массив данных и т. п. Деление виртуального адресного пространства на сегменты осуществляется компилятором на основе указаний программиста или по умолчанию, в соответствии с принятыми в системе соглашениями. Максимальный размер сегмента определяется разрядностью виртуального адреса, например при 32-разрядной организации процессора он равен 4 Гбайт. При этом максимально возможное виртуальное адресное пространство процесса представляет собой набор из N виртуальных сегментов, каждый размером по 4 Гбайт. В каждом сегменте виртуальные адреса находятся в диапазоне от 0000000016 до FFFFFFFF16. Сегменты не упорядочиваются друг относительно друга, так что общего для сегментов линейного виртуального адреса не существует, виртуальный адрес задается парой чисел: номером сегмента и линейным виртуальным адресом внутри сегмента. 1 Реентерабельность (reentrantable) — свойство повторной входимости кода, которое позволяет одновременно использовать его несколькими процессами. При выполнении реентерабельного кода процессы не изменяют его, поэтому в память достаточно загрузить только одну копию кода. Рис. 5.18. Распределение памяти сегментами При загрузке процесса в оперативную память помещается только часть его сегментов, полная копия виртуального адресного пространства находится в дисковой памяти. Для каждого загружаемого сегмента операционная система подыскивает непрерывный участок свободной памяти достаточного размера. Смежные в виртуальной памяти сегменты одного процесса могут занимать в оперативной памяти несмежные участки. Если во время выполнения процесса происходит обращение по виртуальному адресу, относящемуся к сегменту, который в данный момент отсутствует в памяти, то происходит прерывание. ОС приостанавливает активный процесс, запускает на выполнение следующий процесс из очереди, а параллельно организует загрузку нужного сегмента с диска. При отсутствии в памяти места, необходимого для загрузки сегмента, операционная система выбирает сегмент на выгрузку, при этом она использует критерии, аналогичные рассмотренным выше критериям выбора страниц при страничном способе управления памятью. На этапе создания процесса во время загрузки его образа в оперативную память система создает таблицу сегментов процесса (аналогичную таблице страниц), в которой для каждого сегмента указывается: базовый физический адрес сегмента в оперативной памяти; размер сегмента; правила доступа к сегменту; признаки модификации, присутствия и обращения к данному сегменту, а также некоторая другая информация. Если виртуальные адресные пространства нескольких процессов включают один и тот же сегмент, то в таблицах сегментов этих процессов делаются ссылки на один и тот же участок оперативной памяти, в который данный сегмент загружается в единственном экземпляре. Как видно, сегментное распределение памяти имеет очень много общего со страничным распределением. При сегментной организации единицей перемещения между памятью и диском является сегмент, имеющий в общем случае объем больший, чем страница. Однако во многих случаях для работы программы вовсе не требуется загружать весь сегмент целиком, достаточно было бы одной или двух страниц. Аналогично при отсутствии свободного места в памяти не стоит выгружать целый сегмент, когда можно обойтись выгрузкой нескольких страниц. Но главный недостаток сегментного распределения — это фрагментация, которая возникает из-за непредсказуемости размеров сегментов. В процессе работы системы в памяти образуются небольшие участки свободной памяти, в которые не может быть загружен ни один сегмент. Суммарный объем, занимаемый фрагментами, может составить существенную часть общей памяти системы, приводя к ее неэффективному использованию. Система с сегментной организацией функционирует аналогично системе со страничной организацией: при каждом обращении к оперативной памяти выполняется преобразование виртуального адреса в физический, время от времени происходят прерывания, связанные с отсутствием нужных сегментов в памяти, при необходимости освобождения памяти некоторые сегменты выгружаются. Одним из существенных отличий сегментной организации памяти от страничной является возможность задания дифференцированных прав доступа процесса к его сегментам. Например, один сегмент данных, содержащий исходную информацию для приложения, может иметь права доступа «только чтение», а сегмент данных, представляющий результаты, — «чтение и запись». Это свойство дает принципиальное преимущество сегментной модели памяти над страничной.

7Б3В\11Б3В Классификация триггерных схем, примеры, параметры. Основные структуры запоминающих устройств (2D, 3D), структурные методы повышения быстродействия запоминающих устройств.

7Б3В\11Б3В Классификация триггерных схем, примеры, параметры. Основные структуры запоминающих устройств (2D, 3D), структурные методы повышения быстродействия запоминающих устройств.

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время. Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде. Классификация триггеров Классификация триггеров проводится по признакам логического функционирования и способу записи информации (рис. 3.2).

По логическому функционированию различают триггеры типов RS, D, T, JKи др. Кроме того, используются комбинированные триггеры, в которых совмещаются одновременно несколько типов, и триггеры со сложной входной логикой (группами входов, связанных собой логическими зависимостями). По способу записи информации различают асинхронные (нетактируемые) и синхронные (тактируемые) триггеры. В нетактируемых переход в новое состояние вызывается непосредственно изменениями входных информационных сигналов. В тактируемых, имеющих специальный вход, переход происходит только при подаче на этот вход тактовых сигналов. Тактовые сигналы называют также синхронизирующими, исполнительными, командными и т.д. Обозначаются они буквой C (от слова Clock). По способу восприятия тактовых сигналов триггеры делятся на управляемые уровнем и управляемые фронтом. Управление уровнем означает, что при одном уровне тактового сигнала триггер воспринимает входные сигналы и реагирует на них, а при другом не воспринимает и остаётся в неизменном состоянии. При управлении фронтом разрешение на переключение даётся только в момент перепада тактового сигнала (на его фронте или спаде). В остальное время независимо от уровня тактового сигнала триггер не воспринимает входные сигналы и остаётся в неизменном состоянии. Триггеры, управляемые фронтом, называют также триггерами с динамическим управлением. По характеру процесса переключения триггеры делятся на одноступенчатые и двухступенчатые. В одноступенчатом триггере переключение в новом состояние происходит сразу, в двухступенчатом – по этапам. Двухступенчатые триггеры состоят из входной и выходной ступеней. Переход в новое состояние происходит в обеих ступенях поочерёдно. Один из уровней тактового сигнала разрешает приём информации во входную ступень при неизменном состоянии выходной ступени. Другой уровень тактового сигнала разрешает передачу нового состояния из входной ступени в выходную. Общность структур особенно проявляется для статических ОЗУ и памяти типа ROM. Структуры динамических ОЗУ имеют свою специфику. Для статических ОЗУ и памяти типа ROM наиболее характерны структуры 2D, 3D и 2DM. Структура 2D В структуре 2D, запоминающие элементы ЗЭ организованы в прямоугольную матрицу размерностью , где М - информационная емкость памяти в битах; k - число хранимых слов; m - их разрядность. Дешифратор адресного кода DC при наличии разрешающего сигнала активизирует одну из выходных линий, разрешая одновременный доступ ко всем элементам выбранной строки, хранящей слово, адрес которого соответствует номеру строки. Направление обмена определяется усилителями чтения/записи под воздействием сигнала R/W (Read/Write).

Структура типа 2D применяется лишь в ЗУ малой информационной емкости, т. к. при росте емкости проявляется несколько ее недостатков, наиболее очевидным из которых является чрезмерное усложнение дешифратора адреса (число выходов дешифратора равно числу хранимых слов).

Структура 3D Структура 3D позволяет резко упростить дешифраторы адреса с помощью двухкоординатной выборки запоминающих элементов. Принцип двухкоординатной выборки поясняется на рисунке 17 на примере ЗУ типа ROM, реализующего только операции чтения данных. Здесь код адреса разрядностью n делится на две половины, каждая из которых декодируется отдельно. Выбивается запоминающий элемент, находящийся на пересечении активных линий выходов обоих дешифраторов. Таких пересечений будет как раз с одноразрядной организацией. Рисунок 17 - Структура ЗУ типа 3D Суммарное число выходов обоих дешифраторов составляет ,что гораздо меньше, чем 2n при реальных значениях n. Уже для ЗУ небольшой емкости видна эта существенная разница: для структуры 2D при хранении 1К слов потребовался бы дешифратор с 1024 выходами, тогда как для структуры типа 3D нужны два дешифратора с 32 выходами каждый. Недостатком структуры 3D в первую очередь является усложнение элементов памяти, имеющих двухкоординатную выборку. Структуры типа 3D имеют также довольно ограниченное применение, поскольку в структурах типа 2DM (2D модифицированная) сочетаются достоинства обеих рассмотренных структур - упрощается дешифрация адреса, и не требуются запоминающие элементы с двухкоординатной выборкой

Структура 3D Структура 3D позволяет резко упростить дешифраторы адреса с помощью двухкоординатной выборки запоминающих элементов. Принцип двухкоординатной выборки поясняется на рисунке 17 на примере ЗУ типа ROM, реализующего только операции чтения данных. Здесь код адреса разрядностью n делится на две половины, каждая из которых декодируется отдельно. Выбивается запоминающий элемент, находящийся на пересечении активных линий выходов обоих дешифраторов. Таких пересечений будет как раз с одноразрядной организацией. Рисунок 17 - Структура ЗУ типа 3D Суммарное число выходов обоих дешифраторов составляет ,что гораздо меньше, чем 2n при реальных значениях n. Уже для ЗУ небольшой емкости видна эта существенная разница: для структуры 2D при хранении 1К слов потребовался бы дешифратор с 1024 выходами, тогда как для структуры типа 3D нужны два дешифратора с 32 выходами каждый. Недостатком структуры 3D в первую очередь является усложнение элементов памяти, имеющих двухкоординатную выборку. Структуры типа 3D имеют также довольно ограниченное применение, поскольку в структурах типа 2DM (2D модифицированная) сочетаются достоинства обеих рассмотренных структур - упрощается дешифрация адреса, и не требуются запоминающие элементы с двухкоординатной выборкой