Классификация запоминающих устройств и устройства

Содержание

| Триггеры rs и rst | |

| Принцип действия | |

| Назначение выводов, обозначение. | |

| Классификация запоминающих устройств и устройства |

Чатсь Первая

Триггеры rs и rst типов

RS-Триггеры

Триггеры представляют собой импульсные устройства, которые характеризуются наличием двух устойчивых состояний. Простейший триггер имеет два входа и два выхода (рис. 1). Выходы обозначают Q и /Q. Выход Q называют прямым, a /Q - инверсным. Уровни напряжения на обоих выходах взаимно инверсны: если сигнал Q = 1, то /Q = 0, либо если Q = 0, то /Q = 1. Необходимо еще отметить, что состояние триггера, при котором Q = 1, a /Q = 0, называют единичным. При нулевом состоянии триггера Q = 0 и /Q = 1. С поступлением сигналов на входы триггера в зависимости от его состояния либо происходит переключение, либо исходное состояние сохраняется. В зависимости от функциональной связи между логическими сигналами на входах и выходах триггеры в интегральном исполнении имеют следующие наименования: /R/S, RS, D, Т, JK и некоторые другие. Теми же буквами обозначают и входы триггеров.

Рис. 1. /R/S-триггер: А - временная диаграмма работы, Б - условное графическое обозначение, В - схема с двумя ЛЭ И-НЕ

На рис. 4.1 показан простейший триггер - типа /R/S. Здесь использованы только два ЛЭ И-НЕ. Назначение входов: /S-для установки триггера в единичное состояние и /R - для возвращения в нулевое состояние. Черточки над обозначениями входов показывают, что переключение триггера происходит, когда входное напряжение высокого уровня сменяется напряжением низкого уровня (рис. 1, а). Нетрудно видеть, что когда на входы не поступают сигналы, триггер сохраняет свое состояние. Если, например, Q = 1 и /Q = 0, т. е. триггер в единичном состоянии, то, поскольку выход DD1 связан с одним из входов DD2, а выход DD2 - с одним из входов DD1, на двух входах DD2 действует напряжение высокого, а на выходе - низкого (/Q = 0) уровня. В то же время на одном из входов DD1 напряжение низкого, а на выходе - высокого уровня. Если теперь на вход /S поступает сигнал с обозначенной полярностью (момент t1, рис. 1, а), состояние триггера не изменится, потому что поступление сигнала на второй вход DD1 временно изменит только сочетание сигналов на входах (до подачи сигнала оно было 1 и 0, а стало 0 и 0), но выходное состояние DD1 остается при этом неизменным. Если, однако, сигнал поступит на вход /R (момент t2), на обоих входах DD2 уже окажутся напряжения разного уровня, состояние ЛЭ изменится и на выходе его будет напряжение высокого уровня. На обоих входах DD1 окажутся напряжения высокого уровня, а на выходе - низкого, т. е. триггер "опрокинется" и перейдет в другое состояние: Q =О и /Q = 1.

Из сказанного следует, что смена состояния триггера происходит только при чередовании сигналов низкого уровня на входах /S и /R. При этом, если такие сигналы поступят на оба входа одновременно, то после их прекращения состояние триггера станет неопределенным (состояние Q = 0 или Q = 1 равновероятно). Поэтому одновременная подача сигналов низкого уровня на оба входа не разрешается.

Принцип действия.

Работа /R/S-триггера характеризуется таблицей состояний (индексы n и n+1 означают принадлежность сигнала моменту времени tn и следующему за ним tn+1):

| /Rn | /Sn | Qn+1 | /Qn+1 |

| Qn | /Qn | ||

| неопределенное состояние |

Не разрешается одновременная подача напряжения низкого уровня на оба входа /R/S-триггера.

Триггер типа RS, как и /R/S-триггер, "запоминает", на какой из двух входов (R или S) поступил последний сигнал: если на вход R, триггер находится в нулевом состоянии (Q = 0 и /Q = 1), а если на вход S, то в единичном состоянии (Q = 1 и /Q = 0).

Рис. 2. RS-триггер: А - временная диаграмма работы, Б - условное графическое обозначение, В - схема с четырмя ЛЭ И-НЕ.

На рис. 2 показана схема RS-триггера, выполненного на ЛЭ И-НЕ. Она отличается от схемы /R/S-триггера тем, что к каждому входу добавлено по инвертору (DD3 и DD4), которые только обеспечивают необходимый уровень входных сигналов.

Изменение входных сигналов от низкого уровня до высокого приводит к смене состояния триггера (моменты t1, t2, t2 и t5; в момент t4 опрокидывания не происходит, так как триггер уже установлен в единичное состояние в предшествующий момент - t3).

Все сказанное относительно RS-триггера сохраняет силу и для /R/S-триггера. Единственное различие касается инверсии уровней входных сигналов (R вместо /R и S вместо /S).

Работа RS-триггера характеризуется следующей таблицей состояний:

| Rn | Sn | Qn+1 | /Qn+1 |

| Qn | /Qn | ||

| неопределенное состояние |

Триггер RSТ-типа (Счётный триггер)

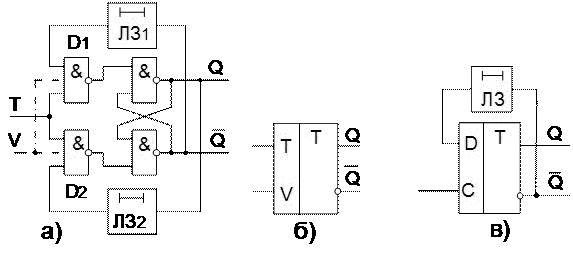

RSТ-триггер или счётный триггер, имеет один счётный вход Т и два выхода (Рисунок 3,а). Функционирование триггера определяется уравнением:

Из уравнения следует, что RSТ-триггер каждый раз изменяет своё состояние на противоположное с приходом на счётный вход Т очередного тактирующего импульса длительностью tи. Этому способствует наличие перекрёстных обратных связей с выходов триггера на входы элементов D1 и D2. Для надёжной работы триггера, с целью сохранения информации о предыдущем состоянии триггера в момент его переключения, в схему вводят элементы задержки, имеющие время задержкиtз>tи.

Рисунок 3 RSТ -триггеры: — а) структурная схема, б) УГО TV-триггера,

в) RSТ-триггер на основе D-триггера.

По окончании действия тактирующего импульса.

Пусть в исходном состоянии Q=1. Сигнал T=1 откроет элемент D2, так как на втором входе D2 имеется сигнал лог «1» с выхода Q, а элемент D1 будет закрыт. Триггер переходит в состояние Q=0. Вентиль D2 остаётся открытым в течение времени tи, т.к. сигнал Q=1 будет задержан ЛЗ1 на время τз>tи. В то же время сигнал  не попадёт на вентиль D1 из-за временной задержки ЛЗ2. При отсутствии элементов задержки возможно неоднократное переключение триггера при условии, если длительность импульса tи значительно превышает время переключения триггера.

не попадёт на вентиль D1 из-за временной задержки ЛЗ2. При отсутствии элементов задержки возможно неоднократное переключение триггера при условии, если длительность импульса tи значительно превышает время переключения триггера.

По окончании действия тактирующего импульса элементы D1 и D2 закроются, так как потенциал входа T=0. После чего на вход элемента D1 через ЛЗ2 поступит сигнал  . В результате с приходом второго импульса T=1 откроется элемент D1 и триггер переключится в состояние Q=1 и т. д.

. В результате с приходом второго импульса T=1 откроется элемент D1 и триггер переключится в состояние Q=1 и т. д.

Роль ЛЗ в Т-триггерах выполняют логические элементы с большим временем задержки tзд.р или специальные компоненты электронных схем, например, диоды с накоплением заряда.

Кроме счётного входа RSТ-триггер может иметь вход разрешения V (Рисунок 50,б). Сигнал на этом входе разрешает (при V=1) или запрещает (при V=0) срабатывание триггера от поступающих на вход T сигналов. Т-триггеры, имеющие дополнительный вход V, называются TV-триггерами. Наличие входа V позволяет организовать счёт в заданном временном интервале, что существенно расширяет функциональные возможности Т-триггера.

Счётный RSТ-триггер может быть построен на основе D-триггера, соединив инверсный выход D-триггера со входом D, как показано на рисунке 50,в. В такой схеме каждый переход 1/0 на входе C будет приводить к переходу триггера в противоположное состояние. Например, если Qn=1, то  , и поэтому очередной тактовый импульс переведёт триггер в новое состояние, т.е. установит Qn+1=Dn=0. Для правильной работы Т-триггера тактовый импульс должен быть коротким, а наличие элемента задержки ЛЗ ослабляет требование к длительности тактового импульса.Таким образом, из рассмотрения принципа работы RSТ-триггера следует, что при Т=1 спадающий фронт сигнала на входе C переводит триггер в противоположное состояние. Частота изменения потенциала на выходе Т-триггера в два раза меньше частоты импульсов на входе C. Это свойство Т-триггеров позволяет строить на их основе двоичные счётчики. Поэтому эти триггеры и называют счётными.

, и поэтому очередной тактовый импульс переведёт триггер в новое состояние, т.е. установит Qn+1=Dn=0. Для правильной работы Т-триггера тактовый импульс должен быть коротким, а наличие элемента задержки ЛЗ ослабляет требование к длительности тактового импульса.Таким образом, из рассмотрения принципа работы RSТ-триггера следует, что при Т=1 спадающий фронт сигнала на входе C переводит триггер в противоположное состояние. Частота изменения потенциала на выходе Т-триггера в два раза меньше частоты импульсов на входе C. Это свойство Т-триггеров позволяет строить на их основе двоичные счётчики. Поэтому эти триггеры и называют счётными.

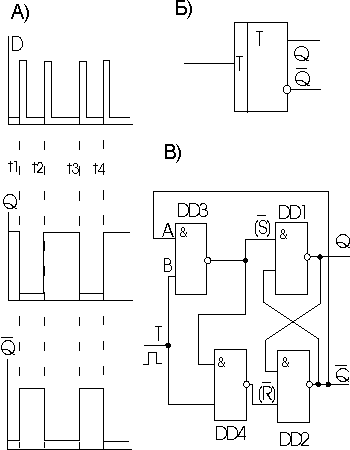

Рис. 4 RSТ-триггер: А - временная диаграмма работы, Б - условное графическое обозначение, В - схема с четырмя ЛЭ И-НЕ

Состояние RST-триггера меняется с поступлением на вход очередного импульса. Таблица состояний RSТ-триггера имеет следующий вид:

| Tn | Qn+1 | /Qn+1 |

| Qn | /Qn | |

| /Qn | Qn |

Назначение выводов, обозначение.

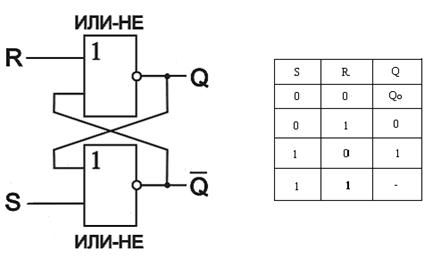

Триггером называется электронное устройство, предназначенное для записи, хранения и считывания двоичной информации. На рис.9.3 изображено условное обозначение асинхронного RS-триггера, в котором происходит переключение из одного устойчивого состояния в другое под действием определённой совокупности раздельных импульсов напряжения на управляющих входах.

Триггер имеет информационные входы R и S , а также информационные выходы: прямой Q и инверсный  . Вход R (от английского слова Reset) является входом установки триггера в состояние лог. 0 , вход S (от английского слова Set) – входом установки триггера в состояние лог.1.

. Вход R (от английского слова Reset) является входом установки триггера в состояние лог. 0 , вход S (от английского слова Set) – входом установки триггера в состояние лог.1.

Рис 4. Условное обозначение асинхронного RS-триггера

На рис 4 приведена структурная логическая схема и таблица истинности RS-триггера, построенного на двух логических элементах ИЛИ-НЕ. Работу RS-триггера иллюстрирует таблица истинности.

Рис 4. Структурная логическая схема и таблица истинности RS-триггера

По таблице истинности видно, что RS-триггер работает только в случаях, когда на информационные входы R и S поступают раздельные сигналы лог.0 и лог.1 (или наоборот). При одновременной подаче на информационные входы R и S лог.0, триггер находится в состоянии хранения предшествующей информации на его информационных выходах. Если же на информационные входы R и Sодновременно поступают сигналы лог.1, то триггер находится в состоянии запрета.

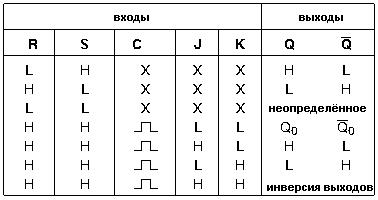

Назначение выводов

Все, что было написано выше, можно посмотреть в таблице истинности для триггера К155ТВ1, которая показана на рисунке 5.

Рисунок 5. Таблица истинности для микросхемы К155ТВ1.

Вторая часть

Классификация запоминающих устройств и устройства

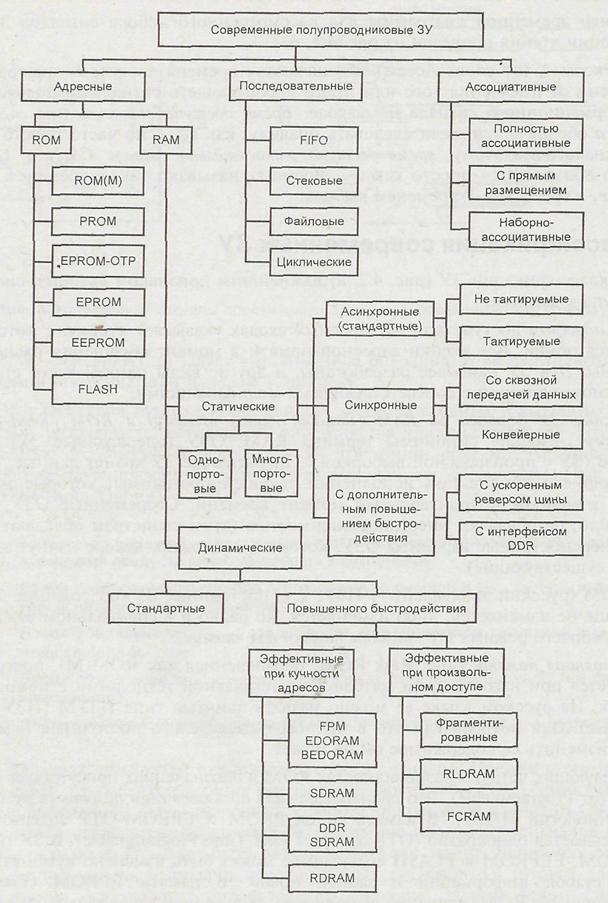

Важнейшим признаком классификации ЗУ (рис. 6) является способ доступа к данным.

Рис. 6 Классификация современных полупроводниковых запоминающих устройств

Все ячейки адресной памяти в момент обращения равнодоступны. Эти ЗУ наиболее разработаны, другие виды памяти часто строят на основе адресной памяти с соответствующими модификациями.

Памятью ЭВМ называется совокупность устройств, служащих для запоминания, хранения и выдачи информации.

Отдельные устройства, входящие в эту совокупность, называются запоминающими устройствами ( ЗУ ) того или иного типа.

Термин " запоминающее устройство " обычно используется, когда речь идет о принципе построения некоторого устройства памяти (например, полупроводниковое ЗУ, ЗУ на жестком магнитном диске и т.п.), а термин "память" - когда хотят подчеркнуть выполняемую устройством памяти логическую функцию или место расположения в составе оборудования ЭВМ (например,оперативная память - ОП, внешняя память и т.п.). В тех вопросах, где эти отличия не имеют принципиального значения, термины "память" и " запоминающее устройство " мы будем использовать как синонимы.

Запоминающие устройства играют важную роль в общей структуре ЭВМ. По некоторым оценкам производительность компьютера на разных классах задач на 40-50% определяется характеристиками ЗУ различных типов, входящих в его состав.

К основным параметрам, характеризующим запоминающие устройства, относятся емкость и быстродействие.

Емкость памяти - это максимальное количество данных, которое в ней может храниться.

Емкость запоминающего устройства измеряется количеством адресуемых элементов (ячеек) ЗУ и длиной ячейки в битах. В настоящее время практически все запоминающие устройства в качестве минимально адресуемого элемента используют 1 байт (1байт = 8 двоичных разрядов (бит)). Поэтому емкость памяти обычно определяется в байтах, килобайтах (1Кбайт=210 байт), мегабайтах (1Мбайт = 220 байт), гигабайтах (1Гбайт = 230 байт) и т.д.

За одно обращение к запоминающему устройству производится считывание или запись некоторой единицы данных, называемойсловом, различной для устройств разного типа. Это определяет разную организацию памяти. Например, память объемом 1мегабайт может быть организована как 1М слов по 1 байту, или 512К слов по 2 байта каждое, или 256К слов по 4 байта и т.д.

В то же время, в каждой ЭВМ используется свое понятие машинного слова, которое применяется при определении архитектуры компьютера, в частности при его программировании, и не зависит от размерности слова памяти, используемой для построения данной ЭВМ. Например, компьютеры с архитектурой IBM PC имеют машинное слово длиной 2 байта.

Быстродействие памяти определяется продолжительностью операции обращения, то есть временем, затрачиваемым на поискнужной информации в памяти и на ее считывание, или временем на поиск места в памяти, предназначаемого для хранения данной информации, и на ее запись:

tобр = max(tобр сч, tобр зп)

где tобр сч - быстродействие ЗУ при считывании информации; tобр зп - быстродействие ЗУ при записи.